概要

Vitis ソフトウェア プラットフォーム開発環境

AMD Vitis™ ソフトウェア プラットフォームは、FPGA ファブリック、Arm® プロセッサ サブシステム、および AI エンジンを含むデザインを開発するための開発環境です。AMD Vivado™ ML Design Suite と組み合わせて使用することで、より高い抽象度で設計が可能になります。

Vitis ソフトウェア プラットフォームには次のツールが含まれています。

- Vitis エンベデッド – エンベデッド Arm プロセッサ上で実行される C/C++ アプリケーション コードを開発するためのツール。

- コンパイラ/シミュレータ – AI エンジン アレイを使用するデザインの実装に使用。

- Vitis HLS - FPGA ファブリック向けの C/C++ ベースの IP ブロックを開発するためのツール。

- Vitis™ Model Composer – MathWorks Simulink® 環境でデザインを短時間で試行できるモデル ベースのデザイン ツール。

- DSP、Vision、Solver、Ultrasound、BLAS など、パフォーマンスに最適化されたオープンソースのライブラリ関数。これらは FPGA ファブリックや AI エンジンを使用して実装可能。

ツール & ライブラリ

Vitis エンベデッド

Vitis™ エンベデッドは、エンベデッド Arm プロセッサ上で実行されるホスト アプリケーション開発を支援するための、スタンドアロンのエンベデッド ソフトウェア開発パッケージです。

Vitis AIE DSP デザイン ツール

コンパイラとシミュレータ

AMD Versal™ アダプティブ SoC デバイスには AI エンジン アレイが搭載されており、高性能 DSP 機能のリソースと消費電力に最適化した実装が可能になります。FPGA ファブリック リソースと AI エンジンを組み合わせて使用することで、DSP アプリケーションの処理性能や効率を向上させることができます。

AMD の Vitis ツールフローを使用して、DSP アプリケーション向け AI エンジンのハードウェア アクセラレーション機能を活用する方法を習得してください。

Vitis HLS

Vitis™ HLS ツールを使用して、C/C++ で定義した関数を RTL に合成することで、複雑な FPGA アルゴリズムを簡単に作成できます。

このツールは、合成/配置;配線用の Vivado™ ML Design Suite およびヘテロジニアス システムの設計や活用のための Vitis 統合ソフトウェア プラットフォームと密接に統合されています。

Vitis Model Composer

Vitis Model Composer は、MathWorks Simulink® 環境でデザインを短時間で試行できるモデル ベースのデザイン ツールです。

このツールでは、AI エンジン ブロックとプログラマブル ロジック (HDL/HLS) ブロックを組み合わせてデザインを構築し、シミュレーションを実行することも可能です。

Vitis ライブラリ

C/C++ で記述された既存アプリケーションに最小限のコード変更を加えるだけですぐに高速化を実現できる、パフォーマンスに最適化されたオープンソース ライブラリです。

ドメイン特化のアクセラレーション ライブラリをそのまま利用して要件に合わせて変更することも、アルゴリズム構築ブロックとして利用して独自のアクセラレータを開発することも可能です。

ツールの使用

AMD のアダプティブ SoC および FPGA の構築部分に応じて異なる Vitis ツールを使用する必要があります。

| FPGA (プログラマブル ロジック) | ライブ ビデオのスケーリング | AI エンジン |

|---|---|---|

| Vivado Design Suite/Vitis HLS/Vitis Model Composer | Vitis エンベデッド | AIE コンパイラ/シミュレータ/ Vitis Model Composer |

デザイン フロー

Vitis エンベデッド ソフトウェア開発フロー

(従来の FPGA ファミリではエンベデッド SDK と呼ばれていた)

Vivado からプラットフォーム ファイルとしてハードウェアをエクスポート

アプリケーション コードの開発

デバッグとブート イメージの生成

AMD アダプティブ SoC の Arm® エンベデッド プロセッサ サブシステムの C/C++ コード開発は、通常次のフローで行われます。

- ハードウェア エンジニアが、AMD の Vivado™ ML Design Suite を使用してプログラマブル ロジックを設計し、ハードウェアを XSA (Xilinx Support Archive) ファイルとしてエクスポートします。

- その後、ソフトウェア エンジニアが、このハードウェア デザイン情報をターゲット プラットフォームに組み込み、Vitis エンベデッド ソフトウェアを使用してアプリケーションコードを開発します。

開発者は、Vitis エンベデッド ソフトウェア内でシステム レベルのすべての検証を実行して、アプリケーションを起動するためのブート イメージを生成できます。

Vitis ソフトウェア プラットフォームを使用したエンベデッド ソフトウェア アプリケーション開発ワークフローの詳細は、ユーザーガイド (UG1400) のエンベデッド ソフトウェア開発用 Vitis ツールのセクションをご覧ください。

Vitis を使用する全体的な設計フロー

(ハードウェアおよびソフトウェア)

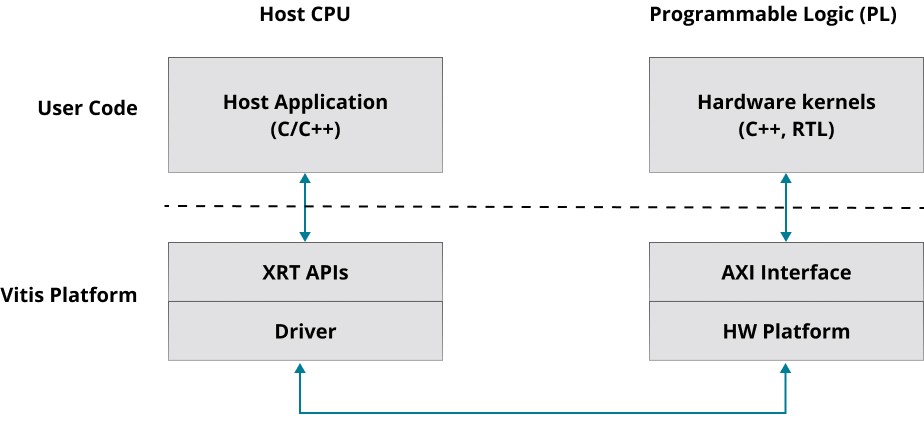

通常、システム設計者が AMD のアダプティブ SoC 内でソフトウェアとハードウェアを統合する場合、このフローを使用します。

このフローは、Arm® エンベデッド プロセッサ上で動作するソフトウェア アプリケーションと、プログラマブル ロジック (PL) と Versal™AI エンジン アレイ上で動作するコンピュート カーネルで構成されるヘテロジニアス エンベデッド システム デザインの開発に使用されます。

フローの構成:

- ソフトウェア ホスト アプリケーションは C/C++ で記述され、通常はエンベデッド Arm プロセッサ サブシステム上で実行されます。ザイリンクス ランタイム ライブラリ (XRT) で実装されたネイティブ API を使用して、AMD デバイス内のハードウェア カーネルとインタラクトします。

- ハードウェア カーネルは、AMD Vitis™ HLS ツールを使用して C++ から生成、あるいは AMD Vivado™ ML Design Suite を使用して RTL で直接記述できます。

Vitis 統合ソフトウェア プラットフォームを使用したヘテロジニアス システムの設計フローの詳細は、ユーザー ガイド (UG1393) のヘテロジニアス システム デザイン用 Vitis ツールのセクションをご覧ください。

AMD Alveo™ データセンター アクセラレータ カードを使用する場合、同じシステム設計フローを使用します。ソフトウェア プログラムは x86 ホスト上で実行され、カーネルは PCIe® で接続されたアクセラレーション カードの FPGA で実行されます。Vitis 統合ソフトウェア プラットフォームを使用したデータセンター アクセラレーション フローの詳細は、ユーザー ガイド (UG1393) のデータセンター アクセラレーション用 Vitis ツールのセクションをご覧ください。

ダウンロード

最新の AMD Vitis™ 統合ソフトウェア プラットフォームをダウンロードしてください。

最新情報

2024.1 の新機能:

AMD Versal™ AI エンジン DSP デザインの改善点

- AI エンジン (AIE/AIE-ML) 向けの強化された DSP およびSolver ライブラリ関数

- AI エンジン シミュレータ機能の使いやすさが向上

AMD Vitis™ 統合ソフトウェア プラットフォームの主な改善点

- 新しいデバイス サポート: AMD Versal™ プレミアム VP1902 アダプティブ SoC、AMD MicroBlaze™ V プロセッサ

- Windows® 環境でのエンベデッド アプリケーション開発および BSP 生成を効率化

- 外部でコンパイルされたエンベデッド アプリケーションのデバッグをユーザーが管理するフロー

- 新しい Bootgen GUI

- プラットフォーム プロジェクトでインクリメンタル ビルドが可能

AMD Vitis IDE (新規 GUI) の主な改善点

- プロセッシング サブシステムの階層型デバッグのサポート

- プロジェクト/ワークスペースのエクスポートおよびインポートのサポート

- Python インタープリターおよび API のサポート

- 新機能のプレビュー ページ

- エンベデッド、AI エンジン、プラットフォーム プロジェクトの新しいファイル変更通知

詳細は、「最新情報」ページをご覧ください。