Vitis ソフトウェア プラットフォーム開発環境

AMD Vitis™ ソフトウェア プラットフォームは、FPGA ファブリック、Arm® プロセッサ サブシステム、および AI エンジンを含むデザインを開発するための開発環境です。AMD Vivado™ Design Suite と組み合わせて使用することで、より高い抽象度で設計が可能になります。

Vitis ソフトウェア プラットフォームに含まれるツール

- Vitis エンベデッド – エンベデッド Arm プロセッサ上で実行される C/C++ アプリケーション コードを開発するためのツール。

- コンパイラ/シミュレータ – AI エンジン アレイを使用するデザインの実装に使用。

- Vitis HLS - FPGA ファブリック向けの C/C++ ベースの IP ブロックを開発するためのツール。

- Vitis™ Model Composer – MathWorks Simulink® 環境でデザインを短時間で試行できるモデル ベースのデザイン ツール。

- DSP、Vision、Solver、Ultrasound、BLAS など、パフォーマンスに最適化されたオープンソースのライブラリ関数。これらは FPGA ファブリックや AI エンジンを使用して実装可能。

ツール & ライブラリ

Vitis エンベデッド

Vitis™ エンベデッドは、エンベデッド Arm プロセッサ上で実行されるホスト アプリケーション開発を支援するための、スタンドアロンのエンベデッド ソフトウェア開発パッケージです。

Vitis AIE DSP デザイン ツール

コンパイラとシミュレータ

AMD Versal™ アダプティブ SoC デバイスには、AI エンジン アレイが統合されているため、リソースと消費電力を最小限に抑えて、高性能 DSP 機能を実現できます。 AI エンジンを FPGA ファブリック リソースと組み合わせて使用することで、高性能 DSP アプリケーションを非常に効率的に実装できます。

Vitis HLS

Vitis HLS ツールは C/C++ で定義した関数を RTL に合成することで、複雑な FPGA アルゴリズムを簡単に作成できます。

このツールは、合成/配置配線用の Vivado™ Design Suite、およびヘテロジニアス システム デザインとアプリケーション用の Vitis 統合ソフトウェア プラットフォームの両方に密接に統合されています。

Vitis Model Composer

Vitis Model Composer は、MathWorks Simulink® 環境でデザインを短時間で試行できるモデル ベースのデザイン ツールです。

このツールでは、AI エンジン ブロックとプログラマブル ロジック (HDL/HLS) ブロックを組み合わせてデザインを構築し、シミュレーションを実行することも可能です。

Vitis ライブラリ

C/C++ で記述された既存アプリケーションに最小限のコード変更を加えるだけですぐに高速化を実現できる、パフォーマンスに最適化されたオープンソース ライブラリです。

ドメイン特化のアクセラレーション ライブラリをそのまま利用して要件に合わせて変更することも、アルゴリズム構築ブロックとして利用して独自のアクセラレータを開発することも可能です。

ツールの使用

AMD のアダプティブ SoC および FPGA の構築部分に応じて異なる Vitis ツールを使用する必要があります。

| FPGA (プログラマブル ロジック) | プロセッシング サブシステム | AI エンジン |

|---|---|---|

| Vivado Design Suite/Vitis HLS/Vitis Model Composer | Vitis エンベデッド | AIE コンパイラとシミュレータ/Vitis Model Composer |

デザイン フロー

Vitis エンベデッド ソフトウェア開発フロー

(従来の FPGA ファミリではエンベデッド SDK と呼称)

Vivado からプラットフォーム ファイルとしてハードウェアをエクスポート |

アプリケーション コードの開発

|

デバッグとブート イメージの生成 |

AMD アダプティブ SoC の Arm® エンベデッド プロセッサ サブシステムの C/C++ コード開発は、通常次のフローで行われます。

- ハードウェア エンジニアが、AMD Vivado™ ML Design Suite を使用してプログラマブル ロジックを設計し、ハードウェアを XSA (Xilinx Support Archive) ファイルとしてエクスポートします。

- その後、ソフトウェア エンジニアが、このハードウェア デザイン情報をターゲット プラットフォームに組み込み、Vitis エンベデッド ソフトウェアを使用してアプリケーションコードを開発します。

開発者は、Vitis エンベデッド ソフトウェア内でシステム レベルのすべての検証を実行して、アプリケーションを起動するためのブート イメージを生成できます。

Vitis ソフトウェア プラットフォームを使用したエンベデッド ソフトウェア アプリケーション開発のワークフローの詳細は、ユーザーガイド (UG1400) のエンベデッド ソフトウェア開発用 Vitis ツールのセクションを参照してください。

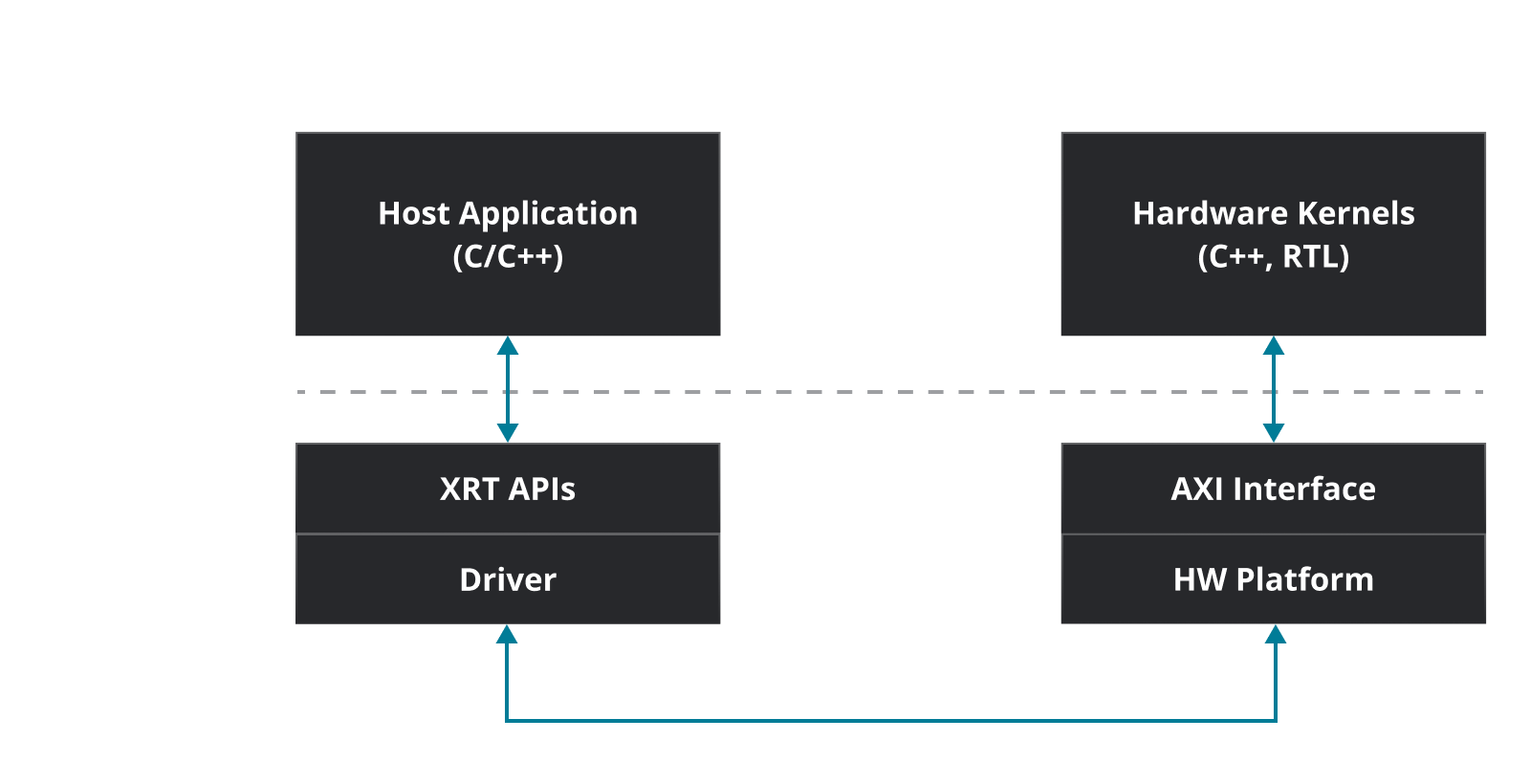

Vitis を使用するシステム デザイン フロー

(ハードウェアおよびソフトウェア)

通常、システム設計者が AMD のアダプティブ SoC 内でソフトウェアとハードウェアを統合する場合、このフローを使用します。

このフローは、Arm® エンベデッド プロセッサ上で動作するソフトウェア アプリケーションと、プログラマブル ロジック (PL) と Versal™AI エンジン アレイ上で動作するコンピュート カーネルで構成されるヘテロジニアス エンベデッド システム デザインの開発に使用されます。

このフローの内容:

- ソフトウェア ホスト アプリケーションは C/C++ で記述され、通常はエンベデッド Arm プロセッサ サブシステム上で実行されます。このアプリケーションは、AMD Vitis ランタイム ライブラリで提供されるネイティブ API を利用して、AMD デバイス内のハードウェア カーネルと相互作用します。

- ハードウェア カーネルは、AMD Vitis™ HLS ツールを使用して C++ から生成、あるいは AMD Vivado™ ML Design Suite を使用して RTL で直接記述できます。

Vitis 統合ソフトウェア プラットフォームを使用したヘテロジニアス システムのデザイン フローの詳細は、ユーザーガイド (UG1393) のヘテロジニアス システム デザイン用の Vitis ツールのセクションを参照してください。

AMD Alveo™ データセンター アクセラレータ カードを使用する場合、同じシステム設計フローを使用します。ソフトウェア プログラムは x86 ホスト上で実行され、カーネルは PCIe® で接続されたアクセラレーション カードの FPGA で実行されます。Vitis 統合ソフトウェア プラットフォームを使用したデータセンター アクセラレーション フローの詳細は、ユーザーガイド (UG1393) のデータセンター アクセラレーション用の Vitis ツールのセクションを参照してください。

2024.2 の新機能

AMD Versal™ AI エンジン DSP デザインの改善点

- Vitis アナライザーを使用したレイテンシとスループットの見積もり

- Vitis アナライザーを使用した利用可能な PLIO の識別

- ヒープ/スタック メモリおよびプロラム メモリのレポート生成

- Versal AI Engine デザインのプロトタイプ作成を加速する新しいフロー

AI エンジン向けの新規および強化された Vitis ライブラリ関数

- AIE 搭載 Versal AI コア シリーズ向けの強化された DSP ライブラリ関数: TDM FIR フィルター、より高性能な GEMM/GEMV、2D IFFT

- AIE ML 搭載 Versal AI エッジ シリーズ向けの新しい DSP ライブラリ関数: TDM FIR フィルター、Radix-3/Radix-5 FFT をサポート、GEMM/GEMV

AMD Vitis IDE の主な改善点 (GUI の刷新)

- 新しいシリアル端子: ハードウェアからのシリアル メッセージを監視可能

- 拡張機能マーケットプレイス – サードパーティの拡張機能を検索してインストール可能

- PS トレース – エンベデッド システムのデバッグや性能最適化を支援する新機能

詳細は、「新機能」および「AMD Vitis IDE」のページをご覧ください。