Software Defined

注: 2019.2 のリリースより、AMD SDK、SDSoC™ および SDAccel™ 開発環境は、アプリケーション アクセラレーションおよびエンベデッド開発をサポートする、Vitis™ 統合ソフトウェアプラットフォーム に統合されます。このため、AMD SDAccel 開発環境の 2019.2 以降のリリースはありません。

概要

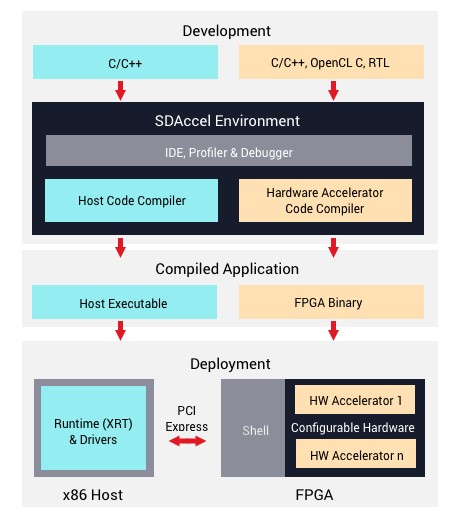

SDAccel™ 環境は、AMD の Alveo データセンター アクセラレータ カード、AWS F1 インスタンス、およびその他の FPGA-as-a-Service (サービスとしての FPGA) 製品をターゲットとするアプリケーション向けの統合開発環境です。

次を備えた使い慣れた環境を提供します。

- 統合開発環境 (IDE)

- アプリケーションの最適化をサポートするプロファイラー

- ホスト コードおよび FPGA アクセラレーション コード用コンパイラ

- 迅速な開発とデバッグを可能にするエミュレーション フロー

- ソフトウェアとハードウェア間の自動通信

ホスト アプリケーションは C/C++ で開発され、標準の OpenCL API 呼び出しを使用して RTL、C/C++、または OpenCL のいずれかの言語でモデル化される FPGA アクセラレーション機能と相互作用します。このため、ハードウェア設計者とソフトウェア設計者の両者が使い慣れた環境で作業できます。

SDAccel IDE は、ホスト アプリケーション向けの最適化されたコンパイラ、適応型ハードウェア向けのクロス コンパイラ、堅牢なデバッグ環境、性能の問題点を特定してアプリケーションを最適化するプロファイラーなど、標準的なソフトウェア開発環境の機能をすべて備えています。

ザイリンクス ランタイム (XRT) とボード固有のシェルにより、FPGA アクセラレータとホスト アプリケーション間の通信は自動的に処理されます。ソフトウェア開発者がこれら接続の詳細を指定する必要はありません。

長所

適応型ハードウェア アクセラレーションの利点

- 10 倍 ~ 1000 倍の性能向上*

- レイテンシの削減

- 消費電力の削減

- CPU 時間の短縮

- SDAccel 開発環境によるシンプルな開発フロー

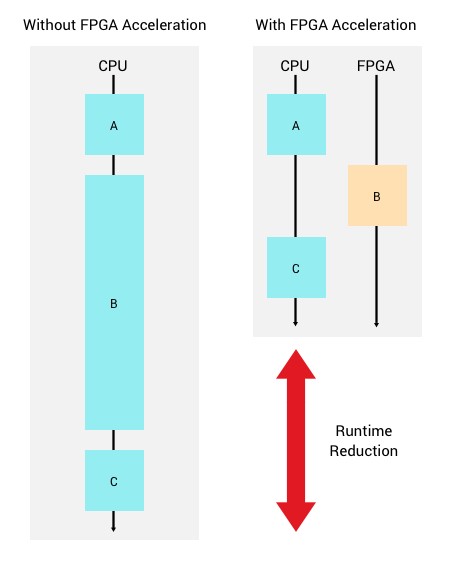

AMD の FPGA/ACAP デバイスは、高性能アルゴリズムおよびワークロードを低レイテンシで高速化するのに最適なソリューションです。

アムダールの法則と相まって、ムーアの法則とデナード スケーリングが衰退する中、現在では最高性能、最小レイテンシ、最小電力でアプリケーションの高速化を目指す開発者にとって DSA (設計固有のアーキテクチャ) が最適な手段として考えられるようになってきました。

汎用 CPU や GPU とは異なり、FPGA および ACAP デバイスは適応性があるため、DSA を構築してコードの特定部分を高速化できます。

SDAccel 開発環境は、ホスト アプリケーションの性能をプロファイリングし、高速化の可能性を判断するための包括的なツールとレポートを提供します。

このようなツールを使用することで、キャッシュ、メモリ、バス使用状況のランタイム計測が自動化されるため、ハードウェア上でのリアルタイム性能を追跡できます。

* 10 倍 ~ 1000 倍の性能向上はアプリケーションに依存します。

主な資料

SDAccel

Alveo 向け SDAccel ライセンス

注記: 既に Vivado HLx のライセンスをご購入済みの方は、アカウントから AWS F1 オンプレミス開発用の無償ライセンスをご利用いただけます。

2018.2 XDF Edition のリリースより、すべての SDAccel の 30 日間無償評価版を提供しています。ソフトウェアをダウンロードして、インストール終了時に無償評価版を選択してください。