- テクノロジ

- 電力効率

AMD は、シリコン プロセスや省電力アーキテクチャを慎重に選定し、Spartan™ 6、7 シリーズ、UltraScale™、および UltraScale+™ FPGA/アダプティブ SoC を含むすべての製品ポートフォリオで電力の効率化を実現しています。世代を追うごとに、プロセス技術、アーキテクチャの革新、高度な電力制御、高度なソフトウェア最適化など、消費電力を削減するためのさまざまな機能が拡充されています。機能、シリコン プロセスの特長、ベンチマーク比較の詳細をポートフォリオ別に示します。消費電力の見積もり、熱モデル、ソフトウェアでの完全なサポート、デモ ボードは、全ファミリで対応しています。AMD デバイスの電源設計向けには、アダプティブ SoC、SoC、または FPGA の機能を最大限に活用するための包括的な資料、検証済みリファレンス デザイン、さらには画期的な設計ツールを提供しています。

Versal アダプティブ SoC

TSMC の 7 nm HK-MG FinFET プロセスを採用しているの次世代ヘテロジニアス コンピューティング デバイス Versal™ アダプティブ SoC は、革新的なアーキテクチャと電力最適化ブロックにより、かつてないレベルの低電力と高性能を達成できます。Versal AI エンジン アーキテクチャは、計算負荷の高いアプリケーションで最大 40% の省電力化を実現

- ハード化された BRAM、URAM、および DSP ブロックにより、デバイスの効率が向上

- より効率的な DSP ブロックで、複雑な浮動小数点演算性能を強化

- パワー ゲーティングにより、使用していないブロック RAM のリーク電流を削減

- URAM の初期化やその幅が設定可能でなり、外部 RAM/ROM の必要性が減少

ハード ブロックとプログラマブル ブロックを併せ持つ Versal アダプティブ SoC は、前世代の省電力メリットに加えて、ワットあたり最高の性能を実現します。また、改善された電力管理、新しい電圧/周波数スケーリング技術、システム モニターの統合により、必要な場合にのみ電力を消費するインテリジェントな電力管理を可能にします。

UltraScale+ FPGA

高性能で低消費電力の半導体プロセス (TSMC 社の 16 nm FinFET) を採用している UltraScale+ デバイスは、7 シリーズ FPGA や SoC と比較してデバイス レベル消費電力を最大 60% 削減できます。アーキテクチャの革新は次のとおりです。

- ハードウェアベースのクロック ゲーティング

- ハード化されたブロック RAM カスケード

- DSP ブロックの効率

- 消費電力の削減に最適化されたトランシーバー

アーキテクチャの革新およびコア ファブリックのデュアル電圧動作によって消費電力を削減すると同時に性能を向上させることで、UltraScale+ ファミリは 7 シリーズ ファミリよりも、単位ワットあたりの性能を 2 倍以上向上させることができます。

UltraScale+ FPGA 消費電力削減

| 7 シリーズ (28 nm) VNOM |

UltraScale (20 nm) VNOM |

UltraScale+ (16 nm) VNOM |

UltraScale+ (16 nm) VLOW |

|

|---|---|---|---|---|

| 動作電圧 (VCCINT) | 1V | 0.95V | 0.85V | 0.72V |

| 正規化後のファブリック性能 | 1.0x | 1.2x | 1.6x | 1.2x |

| 総消費電力 (標準) | 1.0x | 0.7x | 0.8x | 0.5x |

| 単位ワットあたりの性能 | 1.0x | 1.7x | 2x | 2.4x |

Zynq UltraScale+ MPSoC

UltraScale+ FPGA ロジックの消費電力削減機能のほかにも、Zynq™ UltraScale+ MPSoC は、プロセッシング システム内の複数の電源アイランドやドメインを利用して、粗粒度/細粒度でダイナミック消費電力を削減するパワー ゲーティングを適用することで、パフォーマンス要件に応じて消費電力を頻繁に調整してデバイス全体の消費電力を削減します。

UltraScale FPGA

TSMC の低消費電力 20 nm 半導体プロセスを採用し、スタティック消費電力とダイナミック消費電力を削減するパワー ゲーティング機能を備えた UltraScale FPGA ファミリは、7 シリーズ FPGA よりもデバイスレベルの総消費電力を最大 40% 抑えることができます。UltraScale+ デバイスに適用されているアーキテクチャの革新は次のとおりです。

- ハードウェアベースのクロック ゲーティング

- ハード化されたブロック RAM カスケード

- DSP ブロックの効率

- 消費電力の削減に最適化されたトランシーバー

UltraScale 消費電力削減

| 7 シリーズ (28 nm) VNOM |

UltraScale (20 nm) VNOM |

UltraScale+ (16 nm) VNOM |

UltraScale+ (16 nm) VLOW |

|

|---|---|---|---|---|

| 動作電圧 (VCCINT) | 1V | 0.95V | 0.85V | 0.72V |

| 正規化後のファブリック性能 | 1.0x | 1.2x | 1.6x | 1.2x |

| 総消費電力 (標準) | 1.0x | 0.7x | 0.8x | 0.5x |

| 単位ワットあたりの性能 | 1.0x | 1.7x | 2x | 2.4x |

7 シリーズ FPGA および Zynq 7000 SoC

高性能かつ低電力なプロセス技術 (28HPL) で構築されたわずか 28 nm の FPGA/SoC ファミリの 7 シリーズ デバイスおよび Zynq 7000 SoC は、前世代ファミリよりも総消費電力を最大 50% 削減でき、競合の 28 nm ソリューションよりも優れた性能 (ワットあたり) を実現できます。アーキテクチャおよびブロックレベルの革新は次のとおりです。

- スタティック消費電力を削減する Dynamic Function eXchange (DFX)

- マルチモードの I/O 制御

- インテリジェント クロック ゲーティング

- パワー ビニング、電圧スケーリング

優位性のあるベンチマーク サマリおよびベンチマーク プロセスの詳細を参照してください。

最適化された電力管理ソリューション

電力管理の要件は非常に多様化しており、通常、顧客デザインに特有のものとなります。つまり、1 つの電力管理デザインでは最適なソリューションを提供できません。AMD は、業界最先端の電力管理ソリューションを提供する企業 (次のリスト参照) と提携し、一般的なユース ケースに対応するさまざまなリファレンス デザインおよび AMD 製品の電源要件に関する全体的なガイダンスを提供しています。

ハードウェア検証済み電力管理ソリューション

ハードウェア検証済み電力管理ソリューションのリファレンス デザインは、ターゲット デバイスまたはデバイス ファミリに対して AMD が定義した消費電力仕様をすべて満たすように設計されています。AMD の電圧、電流、およびシーケンス仕様を満たすように構築され、テストに合格したソリューションです。設計プロセスをサポートするため、各電力管理ソリューションのベンダーが性能データとデザイン ファイルを提供しています。

ハードウェア以外で検証済みのソリューション

ハードウェア以外で検証済みのソリューションは、AMD が定義した消費電力仕様をすべて満たすように設計されているため、ターゲット デバイスまたはデバイス ファミリの要件を満たすことができます。ハードウェアで検証されていませんが、データシートの仕様では検証されています。

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | アダプティブ SoC シリーズ | 電源レールのグループ化 |

|---|---|---|---|

| Analog Devices, Inc | Versal 電力リファレンス デザイン | AI コア、プライム、AI エッジ | 最小限の電源レール |

| MAXREFDES1238 | |||

| Andapt | 低電流 Versal プレミアム向けプログラム可能な電源供給 | プレミアム | 最小限の電源レール |

| 低電流 Versal プレミアム向けプログラム可能な電源供給 | |||

| Monolithic Power Systems | 効率重視の EVREF105A | AI コア、プライム、AI エッジ | 最小限の電源レール |

| サイズ重視の EVXLVA_02-A | |||

| Infineon | EV-121-D | AI コア、プライム、AI エッジ | 最小限の電源レール |

| Renesas | VERSALDEMOZ1 | AI コア、プライム、AI エッジ | 最小限の電源レール |

| ISLVERSALDEMO2Z | 宇宙グレード AI コア、AI エッジ | 完全な電力マネージメント | |

| Texas Instruments | PMP22165 | AI コア、プライム、AI エッジ | 最小限の電源レール |

| Versal XQR 宇宙グレード ADM-VA600 | 宇宙グレード AI コア、AI エッジ | ||

| PMP23227 車載向け電力供給ソリューション | AI コア、プライム、AI エッジ | 最小限の電源レール |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | アダプティブ SoC シリーズ | 電源レールのグループ化 |

|---|---|---|---|

| Analog Devices, Inc | マルチフェーズの PoL デザイン (PS Overdrive 対応) | プレミアム | 最小限の電源レール |

| 高度に統合され、最適化された電力供給ソリューション | 完全な電力マネージメント | ||

| 高効率で電力管理が有効な電源供給 | HBM | 完全な電力マネージメント | |

| Andapt | 低電流 Versal プレミアム向けプログラム可能な電源供給 | プレミアム | 最小限の電源レール |

| 低電流 Versal プレミアム向けプログラム可能な電源供給 | |||

| Monolithic Power Systems | サイズと効率重視のデザイン | プレミアム | 最小限の電源レール、電力管理 |

| AI エッジ (コマーシャル) のサイズに対して最適な電源供給を実現 | AI エッジ | 最小限の電源レール、電力管理 | |

| AI エッジ (オートモーティブ) の最適な電源供給を実現 | |||

| AI エッジ (オートモーティブ) のサイズに対し最適な電源供給を実現 | |||

| Versal HBM の最適な電源供給を実現 | HBM | 最小限の電源レール、電力管理 | |

| Versal HBM のサイズに対し最適な電源供給を実現 |

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | デバイス ファミリ | ターゲット デバイス |

|---|---|---|---|

| Infineon | AMD ZCU111 評価ボード | RFSoC Gen 1 | ZU21 -ZU29 |

| Monolithic Power Systems | EVREF0102A - RFSoC アナログ電力モジュール ボード |

RFSoC Gen 1 | ZU21 - ZU29 |

| EVREF0106 – RFSoC アナログ レール向けに検証された超低ノイズ電力モジュール | すべての RFSoC | すべての RFSoC | |

| Intersil-Renesas | ISL8024DEMO2Z - RFSoC アナログ電力モジュール ボード | RFSoC Gen 1 | ZU21 - ZU29 |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | デバイス ファミリ |

ターゲット デバイス |

|---|---|---|---|

| Monolithic Power Systems | 電力モジュールを使用したサイズ重視のソリューション |

RFSoC Gen 1 | ZU21 - ZU29 |

| 内部シーケンス機能を備えた高度に統合されたソリューション | RFSoC Gen 1 | ZU21 - ZU29 | |

| サイズ重視のモジュール ベース電源ソリューション | RFSoC Gen 2、RFSoC Gen 3 | ZU39 - ZU49 | |

| 効率重視のディスクリート電源ソリューション | RFSoC Gen 2、RFSoC Gen 3 | ZU39 - ZU49 | |

| PMBus 付きモジュラー電力ソリューション | RFSoC Gen 2、RFSoC Gen 3 | ZU39 - ZU49 |

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | ターゲット デバイス |

|---|---|---|

| Infineon | 電源シーケンス機能を統合した、高度に最適化されたスケーラブル PMIC ベースの 12 のソリューション (ユース ケース 1、2、3) | ZU2 - ZU9 |

| Dialog Semiconductor | 完全な電力管理の柔軟性を提供する、コストおよびフットプリント重視のスケーラブルな電力ソリューション (ユース ケース 4)1 | ZU2 - ZU19 |

| Texas Instruments | リモート ラジオ ヘッド (ユース ケース 2)1 | ZU9、ZU15 |

| ZU2 から ZU5 向けに最適化されたスケーラブルな電力ソリューション (ユース ケース 1、2、3、4)1 | ZU2 - ZU5 | |

| Zynq US+ MPSoC デバイス向けのプログラム可能な電力ソリューション (ユース ケース 1、2、3、4)1 |

ZU2 - ZU19 | |

| Intersil-Renesas | 低消費電力アプリケーション向けに高度に最適化されたディスクリートおよびモジュール ベースのソリューション (ユース ケース 1)1 | ZU2、ZU3 |

| 低消費電力アプリケーション向けに高度に最適化されたディスクリートおよびモジュール ベースのソリューション (ユース ケース 2)1 | ZU11、ZU15、ZU17、ZU19 | |

| Monolithic Power Systems | スケーラブル モジュール ベースのソリューション (ユース ケース 1)1 | ZU2 - ZU19 |

| Analog Devices | KnightRider - 自動車 ASIL-D 準拠の電力供給ボード | すべてのオートモティブ ZU+ (XA) |

| NXP | オートモーティブ MPSoC 向け高度に統合された ASIL PMIC ソリューション | ZU2 - ZU15 |

| Andapt | MPSoC 最小限の電源レール グループのプログラム可能な電力供給ソリューション | すべての ZU+ |

| MPSoC 完全な電力管理レール グループのプログラム可能な電力供給ソリューション | すべての ZU+ |

注記 1: Zynq UltraScale+ デバイスのユース ケースの詳細は、UG583 の「Zynq UltraScale+ MPSoC の電源の統合ソリューション」を参照してください。

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | ターゲット デバイス | 電源レールのグループ化 |

|---|---|---|---|

| Monolithic Power Systems | コストとサイズ重視の電力供給 | ZU1 - ZU3 | 最小限の電源レール、電力管理 |

| ベンダー | リファレンス デザイン | 製品ファミリ |

ターゲット デバイス |

|---|---|---|---|

| TDK | エリア重視の電源モジュール ソリューション | Artix UltraScale+ | すべての AU+ |

| Andapt | Artix UltraScale+ 向け低電力 PMIC ソリューション | Artix UltraScale+ | すべての AU+ |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | 製品ファミリ | ターゲット デバイス |

|---|---|---|---|

| Monolithic Power Systems | コストとサイズ重視の電力供給 | Artix UltraScale+ | すべての AU+ |

| Zynq UltraScale+ コスト重視リファレンス デザイン | Zynq UltraScale+ | ZU1/2/3 | |

| Analog Devices | 低コストで最小限の電源レール ソリューション | Artix UltraScale+ | すべての AU+ |

| Empower Semi | FPGA、ASIC、SoC 向けの高性能かつ柔軟なソリューション | Artix UltraScale+ | すべての AU+ |

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | 製品ファミリ | ターゲット デバイス |

|---|---|---|---|

| Intersil/Renesas | AMD VCU128 評価ボード | Virtex UltraScale+ | VU37P/VU19P1 |

| Monolithic Power Systems | エリア重視のモジュール ベース ソリューション (Kintex UltraScale+ 向け) | Kintex UltraScale+ | All KU+ |

| 高電力密度のディスクリート ソリューション | Virtex UltraScale+ | VU19P-VU57P | |

| モジュールを使用する完全統合ソリューション | Virtex UltraScale+ | VU19P-VU57P | |

| Cyntec | Virtex UltraScale+ | VU37P |

|

| Texas Instruments | PMP10555 - PMBus 対応のモバイル無線基地局向け電源ソリューション | Virtex/Kintex UltraScale+ | すべての KU+、VU3P-VU13P |

| Andapt | 最小限の電源レール ソリューション向けのプログラム可能な PMIC | Kintex UltraScale+ | KU3P-KU15P |

| 最小限の電源レール ソリューション向けのプログラム可能な PMIC | Virtex UltraScale+ | VU3P、VU5P、VU7P | |

| 完全な電力管理向けのプログラム可能な PMIC | Virtex UltraScale+ | VU31P、VU33P、VU35P |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | 製品ファミリ | ターゲット デバイス |

|---|---|---|---|

| Monolithic Power Systems | 効率重視の電力供給ソリューション | Virtex UltraScale+ | VU3P-VU13P、VU31P-VU37P |

| サイズ重視の電力供給ソリューション | Virtex UltraScale+ | VU3P-VU13P、VU31P-VU37P | |

| サイズまたは効率重視の電力供給ソリューション | Virtex UltraScale+ | VU19P、VU27P/29P、VU47P/49P、VU57P | |

| 統合型シーケンス機能を備えた電源供給ソリューション | Kintex UltraScale+ | KU3P-KU15P | |

| サイズ重視の電力供給ソリューション | Kintex UltraScale+ | KU3P-KU15P |

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | 製品ファミリ | ターゲット デバイス |

|---|---|---|---|

| Infineon | Avnet Kintex UltraScale 開発ボード | KU040 | |

| Analog Devices | Virtex UltraScale FPGA マルチ 100G 光ネットワーク プラットフォーム | Virtex UltraScale | VU095、VU125、VU160、VU190 |

| Texas Instruments | GTH & GTY シリアル トランシーバー向けの低ノイズ電源 | Kintex UltraScale | KU025-KU115 |

| Virtex UltraScale FPGA 電力ソリューション (Telemetry オプション付き) | Virtex UltraScale | VU065 - VU440 | |

| Kintex UltraScale FPGA 電力ソリューション (Telemetry オプション付き) | Kintex UltraScale | KU025-KU115 | |

| Alpha Data 社、Radiation Hardened 社電力ソリューション (サードパーティ ボード) | 宇宙グレード Kintex UltraScale | XQRKU060 | |

| Renesas | AMD XQRKU060 FPGA 対応の宇宙グレード 消費電力ソリューション | 宇宙グレード Kintex UltraScale | XQRKU060 |

| Andapt | Kintex UltraScale 向けプログラム可能な PMIC | Kintex UltraScale | すべての KU |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | 製品ファミリ | ターゲット デバイス |

|---|---|---|---|

| Monolithic Power Systems | VCCINT を調整可能なサイズ重視の電源モジュール ソリューション | Kintex UltraScale | すべての KU+ |

| ベンダー | リファレンス デザイン | ターゲット デバイス |

|---|---|---|

| Renesas | Avnet 社製 MiniZed ボードを使用したコストおよびエリア重視の Zynq 7000S ソリューション | 7Z007S |

| Zynq 7000 向けのコストとフットプリント重視のスケーラブルでフレキシブルな電源ソリューション | ZC7020 まで | |

| ISL91211AIK-REFZ | すべての Zynq 7000 | |

| Texas Instruments | Zynq 7000 SoC 向けのスケーラブルな統合電源ソリューションのリファレンス デザイン | すべての Zynq 7000 |

| 低電力 Zynq 7000 および DDR3 電力ソリューション | ZC7010、ZC7020 | |

| 高電力 Zynq 7000 電力管理ソリューション | ZC7035、ZC7040 | |

| Zynq 7010 向けにコンパクトで統合された PMIC 電力ソリューション | ZC7010 | |

| EXAR | インダストリアル イーサネット電力管理リファレンス デザイン | ZC7020 |

| Monolithic Power Systems | インダストリアル イーサネット電力管理リファレンス デザイン | ZC7020 |

| Zynq 7000 コスト重視ディスクリート ソリューション | すべての Zynq 7000 | |

| Zynq 7000 サイズ重視モジュール ソリューション | ||

| NXP | Zynq 7020 ZED ボード向けに最適化された電力管理リファレンス デザイン | ZC7020 |

| Analog Devices | Zynq 7000 高速ネットワーキング ソリューション | ZC7100 |

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | ターゲット デバイス |

|---|---|---|

| Texas Instruments | Artix 7 FPGA 向けのスケーラブルな統合電源ソリューションのリファレンス デザイン | すべての Artix 7 |

| Analog Devices, Inc | Artix 7 ARTY 開発ボード | A35T |

| Artix 7 Basys 3 評価ボード | ||

| Renesas | ISL91211A-BIK-REFZ リファレンス ボード | すべての Artix 7 |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | ターゲット デバイス |

|---|---|---|

| Monolithic Power Systems | ディスクリート Artix 7 リファレンス デザイン | XC7A12T - XC7A200T |

| モジュール ベースの Artix 7 リファレンス デザイン |

ハードウェア検証済みリファレンス デザイン

| ベンダー | リファレンス デザイン | ターゲット デバイス |

|---|---|---|

| Monolithic Power Systems | スケーラビリティ、コスト、およびエリア重視の Spartan 7 ソリューション | S6 - S100 |

| 統合型シーケンス機能を備えたディスクリート電源ソリューション | S6 - S100 | |

| Dialog Semiconductor | Spartan 7 向けのコストとフットプリント重視のスケーラブルでフレキシブルな電源ソリューション | S6 - S100 |

| Texas Instruments | Spartan 7 FPGA 向けのスケーラブルな統合電源ソリューションのリファレンス デザイン | すべての Spartan 7 |

Renesas |

Spartan 7 向けのコストとフットプリント重視のスケーラブルでフレキシブルな電源ソリューション | S6 - S100 |

| ISL91211BIK-REF2Z リファレンス ボード | すべての Spartan 7 |

|

| Andapt | ハードウェアで検証済みのリファレンス デザイン | すべての Spartan 7 |

ハードウェア以外で検証済みのリファレンス デザイン

| ベンダー | リファレンス デザイン | ターゲット デバイス |

|---|---|---|

| Analog Devices, Inc. | Artix 7 & Spartan 7 PMIC ソリューション | すべての Artix 7 & Spartan 7 |

| MPS | Spartan 7 コスト重視ディスクリート ソリューション | |

| Spartan 7 サイズ重視モジュール ソリューション |

注記: これらすべてのソリューションは各ベンダーが責任を持つものです。詳細な情報や入手状況などについては各ベンダーへお問い合わせください。

XPE または PDM をベンダー ツールにアップロード

ウェビナーとアプリケーション ノート

| 種類 | ベンダー | 説明 | ターゲット デバイス |

|---|---|---|---|

ウェビナー |

AMD | AMD アダプティブ SoC/FPGA の消費電力を正確に見積もるために開発された Power Design Manager | すべての AECG |

| AMD/MPS | FPGA およびアダプティブ SoC 向け低消費電力デザイン | ||

| Monolithic Power Systems | MPS 電源ソリューションを使用して、業界唯一シングルチップの適応型無線プラットフォームで設計 | Zynq UltraScale+ RFSoC | |

| Texas Instruments | AMD FPGA & SoC の電源供給レールを迅速に設計する方法 | Spartan 7 FPGA、Artix 7 FPGA、Zynq 7000 SoC | |

アプリケーション ノート |

AMD | XAPP1375 - 簡略化された電源シーケンス | すべてのデバイス |

| XAPP1394 - 温度による動的電圧スケーリングの実装 | Versal™ 動的電圧スケーリング デバイス | ||

| onsemi | ASIL-C レベルに準拠する Zynq UltraScale+ MPSoC 向けオートモーティブ電源ソリューション | Zynq UltraScale+ MPSoC | |

| Monolithic Power Systems | MPS 電源モジュールで AMD Zynq UltraScale+ RFSoC にコンパクトで超低ノイズのソリューションを提供 | Zynq UltraScale+ RFSoC |

|

| Renesas | Dialog PMIC を使用した安全機能のオートモーティブ AMD Zynq UltraScale+ MPSoC | Zynq UltraScale+ MPSoC | |

| Texas Instruments | TPS65086x PMIC を使用して AMD Zynq™ UltraScale+™ MPSoC に電力を供給 | Zynq UltraScale+ MPSoC | |

| AMD Versal AI エッジ シリーズの電源設計 | Versal AI エッジ シリーズ |

電力供給ツール

AMD の電源供給ソリューション パートナーは、電源設計、市場投入までの時間、PDN シミュレーションをサポートする直感的に操作できるツールを提供し、電源システムの最適な性能と信頼性を確保します。各ベンダーのツールに AMD スの XPE ファイルをアップロードして、消費電力のシームレスな見積もりや電源供給ソリューションの定義が可能です。

| ベンダー | 説明 | 機能 |

|---|---|---|

| Andapt | WebAmP R.D | FPGA/SoC 電力管理デザイン ツール |

| Flex Power Modules | Flex Power Designer Tool | 電力供給の設計とシミュレーション XPE ファイルをインポート |

| ProGrAnalog | LoadSlammer PDN 検証ツール | ハードウェアでの電源供給ネットワークの評価/検証 |

| Renesas | PowerCompass マルチロード コンフィギュレータおよび iSim | CAD、電源供給の設計、シミュレーション (XPE、XML、および PWR ファイルをインポート) |

| Andapt | WebAmP R.D | FPGA/SoC 電力管理デザイン ツール |

注記: これらすべてのツールにかかわる責任は、各ベンダーが負うものとします。詳細情報および使用方法については各ベンダーへお問い合わせください。

電源供給ソリューション パートナー

- Analog Devices

- Andapt

- Delta/Cyntec

- Empower

- Flex Power Modules

- Infineon

熱設計:

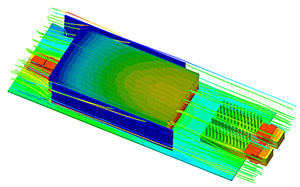

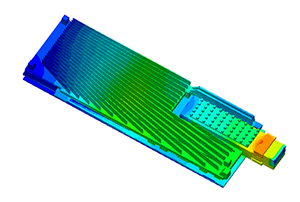

アプリケーションの熱設計の境界線は、アプリケーション タイプやエンド マーケットによって大きく異なります。高性能アプリケーションでの低消費電力設計は、低性能環境での高性能設計と同じ熱管理問題に直面するため、システムの熱管理範囲を把握することは、高性能製品の実現と費用効果の高い製品の実現のいずれにおいても重要です。過剰な熱ソリューション設計は、余分なコストがかかり、デザインを複雑化させてしまいます。

このため、AMD は現在提供している全デバイス対応の DELPHI サーマル モデルを提供しており、これらは Siemens Flotherm と Ansys IcePak の両方をサポートしています。

*Versal アダプティブ SoC モデル (近日公開)

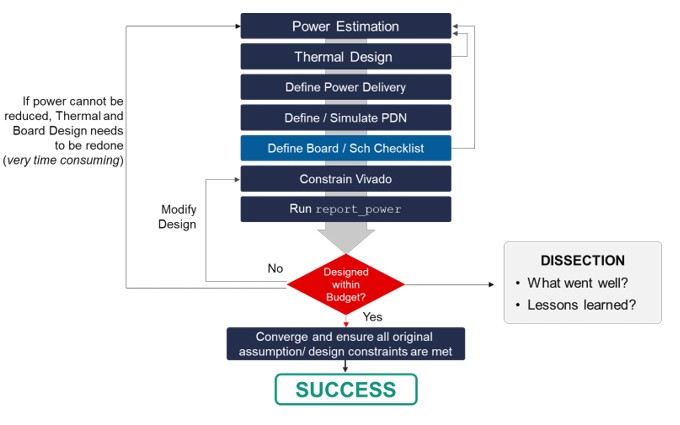

熱シミュレーションはボードを設計する上で不可欠なステップであり、ボード設計プロセスの図に示すように、最初の概算量に基づいて熱管理ソリューションが検証されます。

熱設計ソリューション パートナー

すべてのお客様が熱シミュレーション ツールや熱シミュレーション環境を利用できるわけではありません。AMD アライアンス プログラムへの参加をとおして、熱設計をサポートするパートナーとつながることができます。

パッケージの選択

デバイス選択で重要な点は、最良の熱設計のために適切なパッケージを選択することです。AMD デバイスは、さまざまなユーザー要件に応えるために多くのパッケージ タイプを提供していますが、熱管理性能を考えるとリッドレス パッケージが最適な選択肢となります。AMD デバイスは次のパッケージで提供しています。

ベアダイ – パッケージ指定子 (SB/VB)

- "B はベア ダイを表し、S は 0.8mm、V は 0.92mm のパッケージ ピッチを表します。

リッド付き - (SF/VF)

- "F はフォージド リッドを表し、S は 0.8mm、V は 0.92mm のパッケージ ピッチを表します。

リッドなしパッケージ (VS/LS)

- "S" はスティフナー リングを表し、V は 0.92 mm、L は 1 mm ピッチを表します。

- 最適な熱性能を提供します。

リッドレス オーバーハング パッケージ (VI)

- "I" は、パッケージ オーバーヘッド (パッケージ基板が BGA フットプリントよりも大きい) のあるスティフナ リングを表します。

- "V" は 0.92mm のパッケージ ピッチを表します。

- 最適な熱性能を提供します。

消費電力見積もり

AMD は、インプリメンテーション前の消費電力の見積り、あらゆる設計段階でできるだけ消費電力を削減するように最適化、さらには広範な解析データを提供してユーザーによる最適化を可能にするクラス最高のツールを提供しています。以下に、業界をリードする AMD のすぐに使える消費電力関連ハードウェア/ソフトウェア ベース ツールを示します。