# 2.5D ICs: Just a Stepping Stone or a Long Term Alternative to 3D?

Ivo Bolsens, CTO Xilinx

© Copyright 2011 Xilinx

#### The First Wave of 3D ICs

# ElectronicsWeekly.com IBM Demonstrates 3D Chip Technology in Micron Memory Cube

IBM has announced that Micron will begin production of **Richard Wilson** Friday 02 December 2011 00:01 a memory device built using its commercial CMOS a memory device built using its commercial divides manufacturing technology to employ through-silicon vias (TSVs).

**DRAM Lavers**

Logic Layer

COMPUTERWORLD July 15, 2011 - 5:37 A.M. Apple's A6 processor: 28-nm, 3D IC and made by TSMC

While we wait for Lion, interesting to note the next Apple [AAPL] A6 processor will be made by Taiwan Semiconductor Manufacturing Co. (TSMC) and will be a 3D IC 28-nanometer low-power powerhouse, sweetly tucked inside your iPhones and future model iPads.

#### **EE** Times Perfecting the 3-D chip

R. Colin Johnson 10/11/2011 10:31 AM EDT

You've heard the hype: The foundation of semiconductor fabrication will be transformed over the next few years as multistory structures rise up from dice that today are planar. After almost a decade of major semiconductor engineering efforts worldwide aimed at making the structures manufacturable, three-dimensional ICs are poised for commercialization starting next year-several years behind schedule.

# MercuryNews.com New efforts to extend Moore's Law

#### By Steve Johnson

Continually needing to add computing power to its microprocessors, Santa Clara behemoth Intel (INTC) this year announced it was venturing beyond its traditional method of cramming more and more transistors into a flat pieces of silicon in favor of a different approach -- building chips in three dimensions.

an zuri Xilinx

Micron reveals "Hyper Memory Cube" 3DIC Technology A few weeks ago Mark Durcan, COO of Micron, at the IEEE ISS meeting in Half Moon Bay commented that Micron is "sampling products based on TSVs" and that "Mass production for TSV-based 3-D chips are slated for the next year or 18 month.

THE WALL STREET JOURNAL.

Xilinx Says Four Chips Act

Chip makers have been living by Moore's Law for

for some people, and Xilinx thinks it can help.

decades. But that pace of progress is not fast enough

Intel co-founder Gordon Moore, in the observation that

Silicon Valley residents know by heart, predicted a relentless shrinking of the size and cost of

Like One Giant

components found on ching. The

By Don Clark

transistors turi

# Why Now?

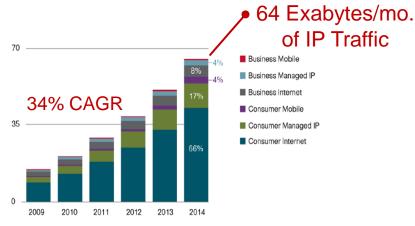

#### Market : Insatiable Bandwidth

Source: Cisco VNI, 2010

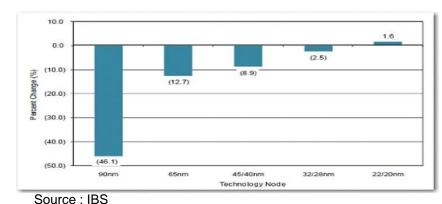

#### Technology : Cost, IO, Power

2014

Multi Tera-Bits System

(1.9Tbps)

400GbE/1TbE

© Copyright 2011 Xilinx

2008

480 Gbps

10GbE, OTU-2

# What Does 3D Buy Us?

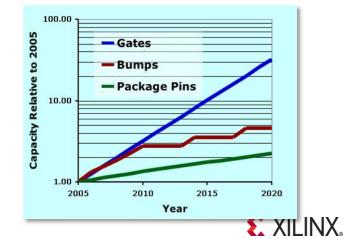

# Connectivity Capacity Crossovers

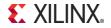

# **Connectivity: Enables High Bandwidth, Low Power Die-to-Die Communication**

#### **100x** bandwidth/watt advantage over conventional methods

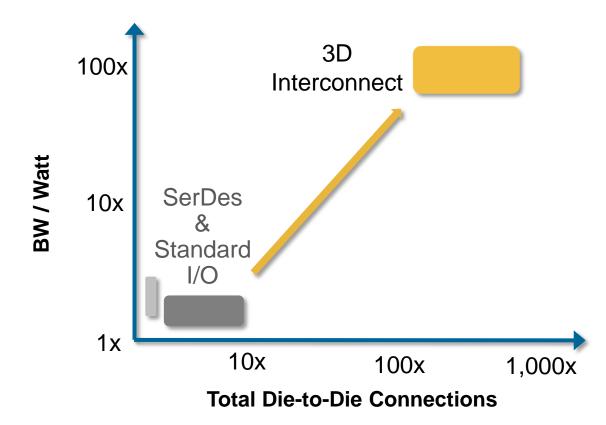

# **Capacity Beyond Moore's Law**

#### **Big Single Monolithic Die**

#### **Multiple Small Die Slices**

✓ Greater capacity, faster yield ramp

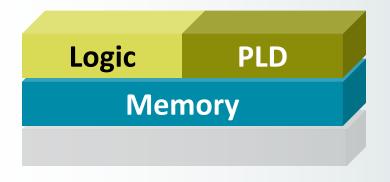

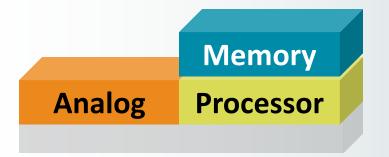

#### "Crossover SoCs" with Heterogeneous Die

#### ✓ Mixed functions

#### ✓ Mixed processes

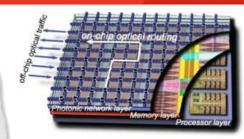

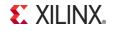

# The Progression of 3D Technology

Flipchip + wire bond

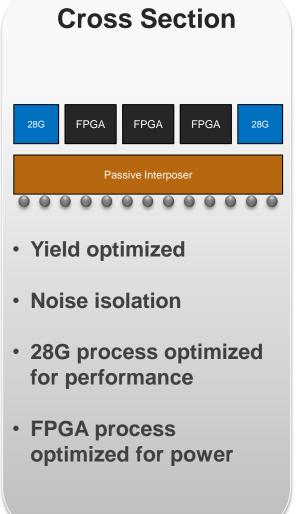

2.5D side-by-side integration with TSVs & silicon interposer

Vertical stacking with memory & logic

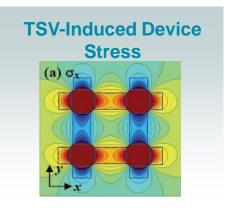

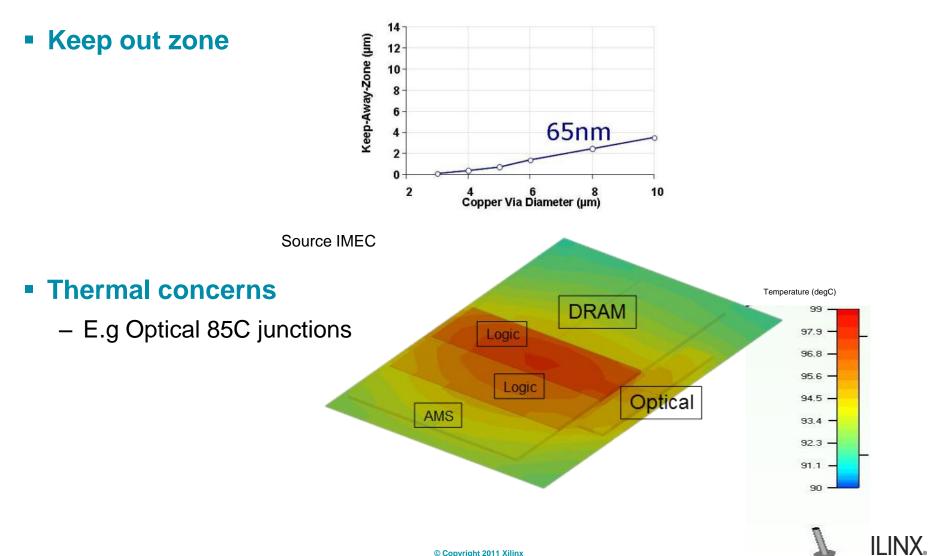

#### **Technical Challenges Posed by 3D**

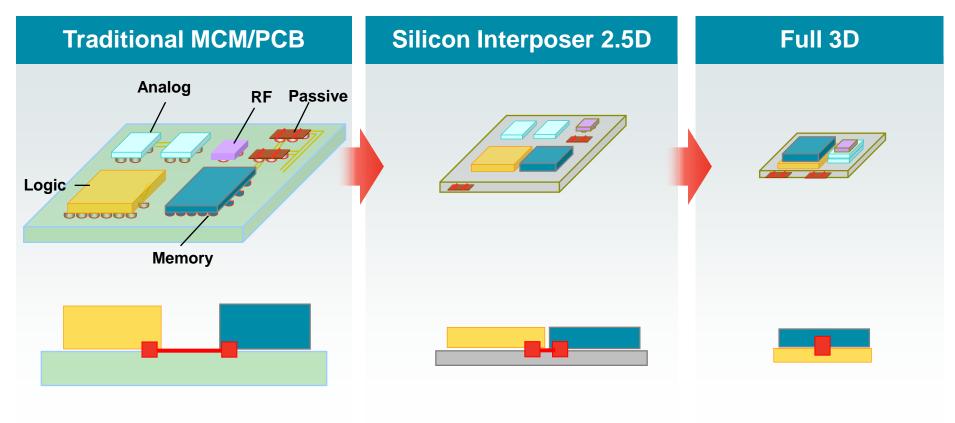

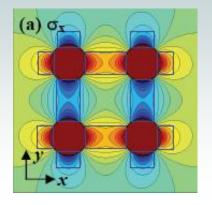

#### **3D – Active on Active**

#### 3D versus 2.5D

|               | 3D            | 2.5D            |

|---------------|---------------|-----------------|

| Design Flow   | New Co-Design | Evolutionary    |

| Testing       | New Methods   | Evolutionary    |

| Cost          | High          | 65nm Interposer |

| Thermal       | Challenging   | Evolutionary    |

| Device Impact | Stress        | None            |

| Reliability   | Challenging   | Evolutionary    |

#### **Case Study: The First 2.5D FPGAs**

© Copyright 2011 Xilinx

# Why FPGA

#### Technology

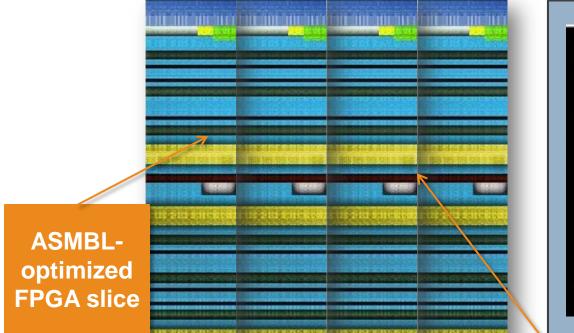

- Column based ASMBL Architecture

- Large Die Integration

- Rich Uniform Programmable Interconnect

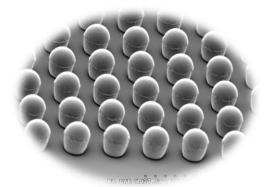

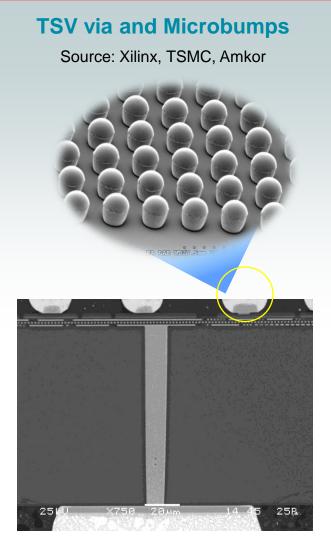

- Tens of Thousands of Microbumps

- Testability

#### Application Domain

- Telecom

- 400Gb Ethernet

- Wide Data path Packet Processing

- Highly Parallel DSP processing

- Highest IO BW (1Terabit/sec by 2014)

- Growing LC capacity (2 M Logic Cells)

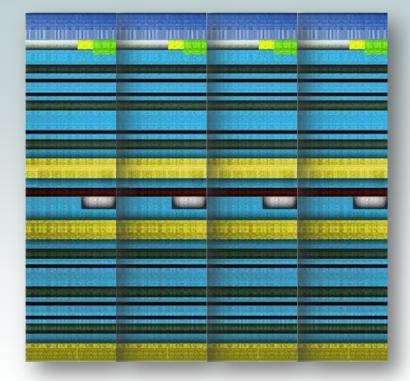

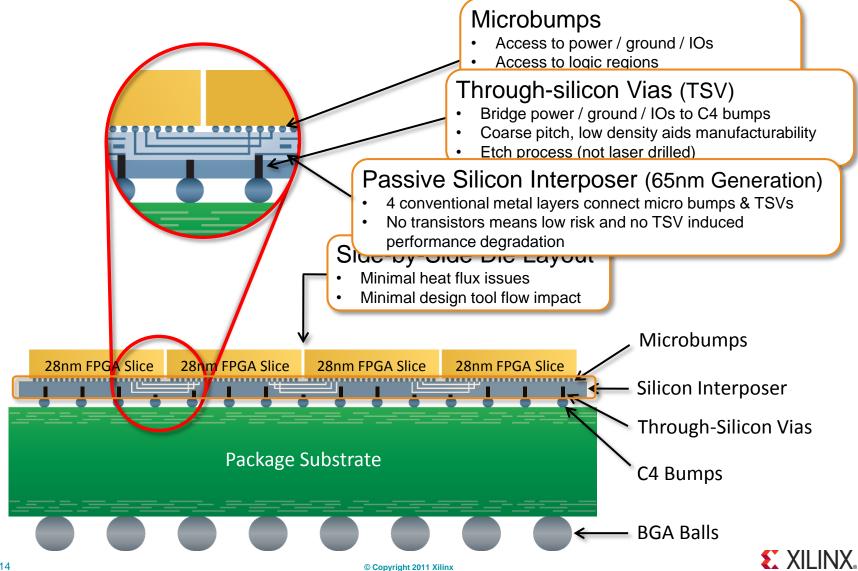

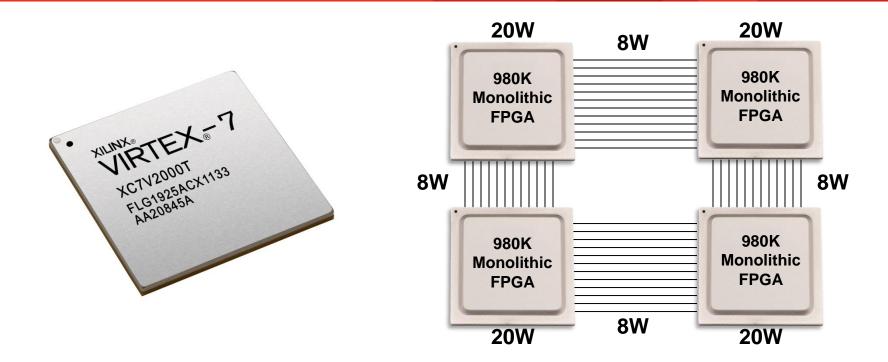

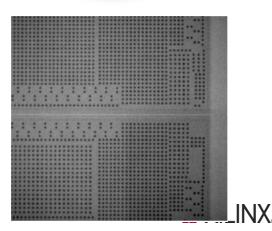

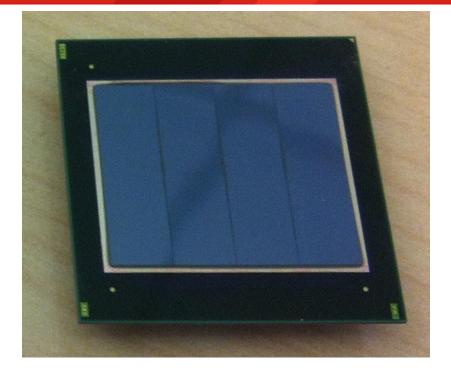

# Virtex-7 2000T

- Virtex 2000T 2 million logic cells

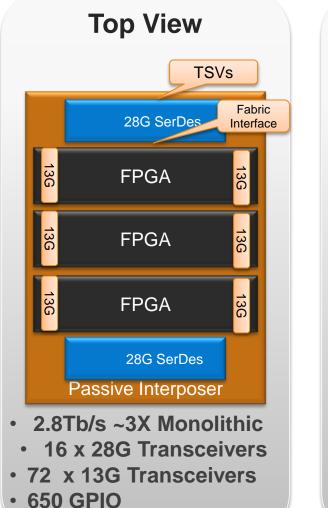

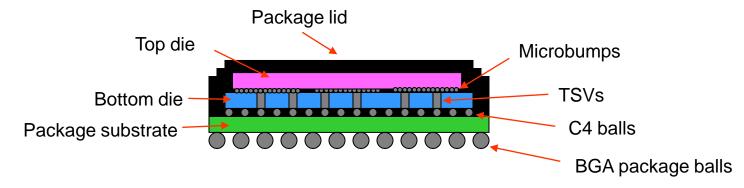

- 4-layer metal Si interposer with TSV

ALC DE

- 4 FPGA sub-die in package

- >10,000 inter-die connections

- Shipping today

#### Harnesses Proven Technology in a Unique Way

#### **Column Based ASMBL Architecture**

FPGA Slices Side-by-Side Segmented Routing High Yields Early

#### Silicon Interposer:

> 10K routing connections between slices

- ~ 1ns latency

- Silicon Interposer

#### Advantages vs. Large Monolithic FPGAs: Capacity and Bandwidth and Power

1 Virtex-7 2000T = 4 Largest Monolithic FPGAs 19 Watts 112 Watts

# **Bandwidth No Equivalent**

## Virtex-7 HT: Heterogeneous 2.5D

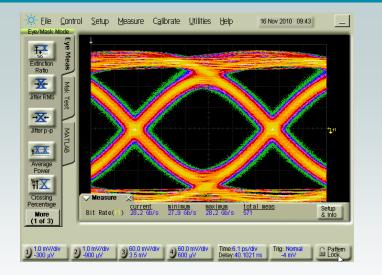

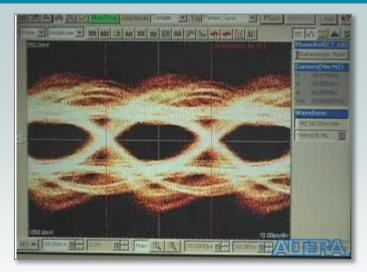

# **Eye Comparison: 2.5D vs. Monolithic**

#### 2.5D Virtex-7 HT @ 28Gbps

#### Other Monolithic FPGA @ 25Gbps

| Parameter      | Virtex-7 HT  | Other Monolithic FPGA |

|----------------|--------------|-----------------------|

| Data Rate      | 28Gb/s       | 25 Gb/s               |

| Data Pattern   | PRBS31       | PRBS7                 |

| Eye Opening    | >2X more     | Less than 1/2         |

| Signal Quality | Clean Jitter | Noisy                 |

© Copyright 2011 Xilinx

# **Evolutionary Technology**

|                              | SSI Package                | Standard Monolithic<br>Flip Chip |  |

|------------------------------|----------------------------|----------------------------------|--|

| Lid                          | Standard (Cu – Ni Plating) | Standard (Cu-Ni Plating)         |  |

| TIM                          | Standard (Silicone)        | Standard (Silicone)              |  |

| uBump                        | Cu Post + Lead free Solder | NA                               |  |

| Chip to interposer underfill | Capillary UF               | NA                               |  |

| Interposer                   | 65 nm Si Technology        | NA                               |  |

| C4 Bump                      | SnPb                       | SnPb                             |  |

| C4 Underfill                 | Capillary UF               | Capillary UF                     |  |

| Package substrate            | Standard (low-CTE Core)    | Standard                         |  |

# **Challenges and FPGA Solutions**

#### <u>Testing</u>

- •Challenge : Probing Microbumps

- Solution : Programmable Interconnect

#### • Thermal

- Challenge : Thermal Conductivity

- Solution : Uniform Spreading of Microbumps

- Design Flow

Leverage Segmented Routing Architecture

#### **Creating the Supply Chain**

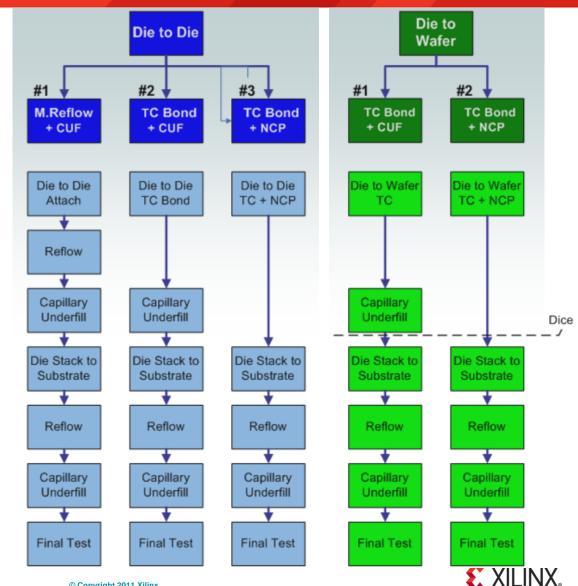

# **Assembly Options Considered**

© Copyright 2011 Xilinx

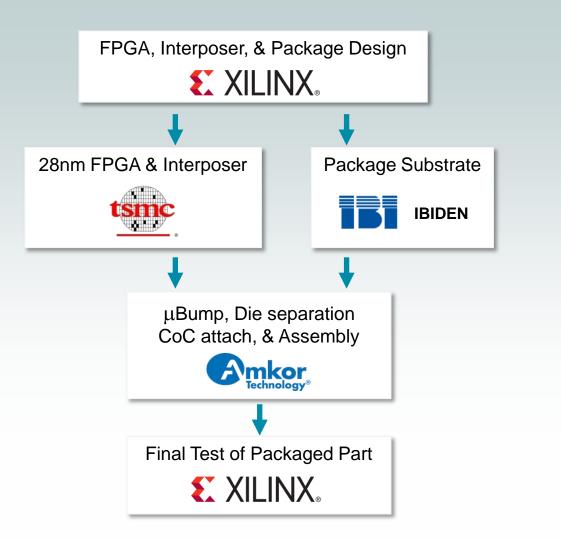

# The Xilinx 2.5-D Supply Chain

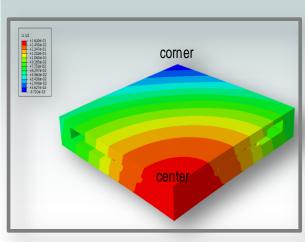

# **3D: The next frontier**

Who's on top?

- High performance chip on on top for thermal and TSV process availability

- Floor-planning critical:

- Thermal concerns (stacked thermal flux)

- TSV keep out zones in bottom die to avoid stress induced performance impact

# **3D Challenges**

© Copyright 2011 Xilinx

# 3D Call-to-Action: Develop & Evolve Standards

#### Design enablement

- Models

- 3D Process Development Kit

#### Manufacturing standards

- DFM rules for TSV, microbump (AR, keep-out)

- Materials TSV, u-bump

- Thermal budget

#### Test

- Test HW

- KGD method

- u-bump probing

#### Interoperability of silicon between fabs

- Shipping methods

- Chip-to-chip Interfaces

# **3D Eco System**

- Leading fabless & fablite companies

- Equipment manufacturers

- Fabs and OSAT

- Industry consortia

- Requirements alignment

- Industry standards setting

- Best practice sharing

# Summary

#### ✓ 3D ICs are here!

Significantly changing the semiconductor landscape

#### ✓ Challenges remain

- Technical and business-related

#### ✓ 2.5D is here to stay

- An important & lower risk path

#### ✓ 3D Call to action

- Industry standards are badly needed

# Stacked Silicon Interconnect: A world of difference

Earth Area: ~500 Million km<sup>2</sup> Population: ~6.8 Billion People Oceans: 5 Age: 5 Billion Years

Virtex-7 2000T Interposer Area: ~775 mm<sup>2</sup> Population: ~6.8 Billion Transistors Chips: 5 Age: 5 weeks