# SmartPHY for DCI and Transport with Versal<sup>™</sup> Premium Series

- > Networked, power-optimized cores deliver 2.2X higher performance/watt vs. competing 10nm FPGAs<sup>1</sup>

- > Scalable SerDes for emerging optical modules and a wide range of client rates and protocols

- > Hardware adaptability for custom bridging and transport functions

## **CHALLENGE**

As data centers move to 400G and beyond, data center interconnect (DCI) technology is at the heart of the cloud-centric world, providing the network capacity for users and applications to connect to compute, network, and storage resources. Bridging various client interfaces to line-side interfaces requires adjusting the SerDes rates and changing the FEC as needed. Due to the mismatch between coherent and clients, the need for multiplexing multiple clients or inverse multiplexing a client over multiple line interfaces has increased in many transport applications. In addition, many data centers are multi-tenant sites that exchange sensitive information, so encryption is required on all interfaces.

# SOLUTION: SMARTPHY FOR DCI AND TRANSPORT WITH VERSAL PREMIUM SERIES

Versal Premium series is a highly integrated, multicore, heterogeneous platform that enables implementation of a single card DCI bridging solution, providing up to 2.4Tb/s of network interfaces to client-side and transport-side optics

(for a total of 4.8Tb/s bi-directional throughput). With the breakthrough integration of connectivity cores and High-Speed Crypto (HSC) Engines, the Xilinx SmartPHY solution implemented on Versal Premium devices provides the highest bridging bandwidth density per device in the industry by far, enabling differentiated products for OEM system providers by accommodating a variety of server-side and transport-side optics and protocols support in a single platform.

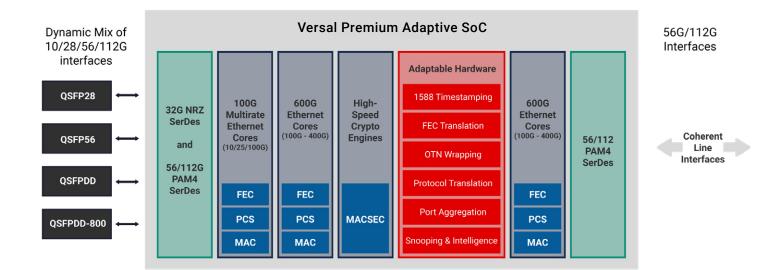

## Scalable SerDes for Diverse Client Interfaces

While coherent optic chipsets are deployed to overcome capacity limitations to provide 400G and beyond, client optics still use 25G NRZ transceivers in many transport applications. Versal Premium devices feature a broad mix of 25G NRZ, 58G PAM4, and 112G PAM4 transceivers to enable unmatched scalability from 10G to 800G to support both existing optics, next-generation NPUs, and coherent ASICs without hardware redesign.

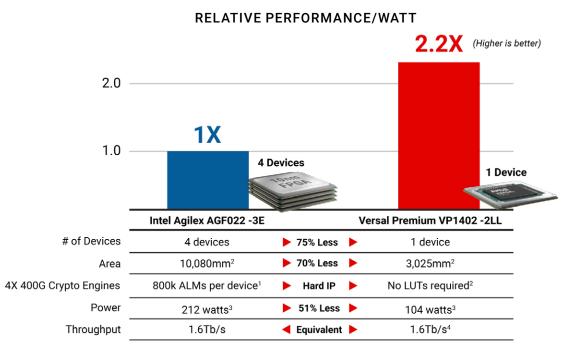

## Dedicated Power-Optimized Hard IP for Greater Performance/Watt

Versal Premium devices integrate power-optimized cores such as 100G/600G Ethernet cores, High-Speed Crypto (HSC) Engines, and integrated PCle® Gen5 with DMA to provide systemlevel advantages, enabling 2.2X performance/watt over competing 10nm FPGAs<sup>1</sup>. Flexible configuration of Ethernet subsystems provides dynamic connectivity for Ethernet/non-Ethernet transponders that use different protocols and multiple FECs without consuming valuable

## Hardware Adaptability Enabling Value Added Features

By integrating dedicated connectivity IP, Versal Premium ACAPs significantly lower logic utilization, retaining more resources for additional functionality such as IEEE Std 1588 timestamping, OTN wrapping, multiplexing, gearboxing, protocol translation, and snooping to address a wide range of dynamic network configurations.

1: Versal Premium VP1402 vs. Intel Agilex AGF022 FPGA implementation

2.2X Performance/Watt<sup>1</sup>

Versal Premium Adaptive SoC for Single-Chip DCI Line Card Implementation

# VERSAL ADAPTIVE SOC IMPLEMENTATION

#### **DCI Bridging and Transport Application**

The SmartPHY solution on the Versal Premium device features heterogeneous engines for efficient implementation, a dedicated connectivity IP for power-optimized interconnect and versatile client interfaces, and adaptable hardware for custom transponder applications to deliver multi-terabit DCI bridging and transport applications. With the right combination of SmartPHY and security technologies in a single platform, hyperscale data center operators and service providers gain the capacity and flexibility to interconnect data centers and build metro / core networks.

| PLATFORM HIGHLIGHTS                      |                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adaptable Engines                        | <ul> <li>Adaptable to a wide range of complex bridging workloads including IEEE Std 1588 timestamping,<br/>OTN wrapping, protocol translation, FEC translation, and more</li> <li>Custom transponders for non-Ethernet clients</li> </ul>                                                                                                                   |

| 100G/600G<br>Ethernet Cores              | <ul> <li>Channelized configuration for signal multiplexing between coherent and client interfaces running at different rates</li> <li>Gearboxing for different electrical connectivity rates</li> <li>Built-in FEC for robust error correction in optical links</li> <li>Stand-alone MAC, FEC, and PCS for OTN or custom protocol implementation</li> </ul> |

| Transceivers                             | <ul> <li>Mix of 32G NRZ, 58G PAM4, and 112G PAM4 transceivers for diverse client interfaces and rates</li> <li>Single-lane 100G deployment for 400G and beyond</li> </ul>                                                                                                                                                                                   |

| High-Speed Crypto<br>(HSC) Engines       | <ul> <li>&gt; Up to 1.6Tb/s of line-rate encryption throughput</li> <li>&gt; AES-GCM-256/128 engine for encryption/decryption</li> <li>&gt; 400G of MACsec, IPsec, and bulk encryption per engine for DCI-optimized security</li> </ul>                                                                                                                     |

| Programmable<br>Network on Chip<br>(NoC) | <ul> <li>Seamless on-chip data movement for all engines and key interfaces</li> <li>Simplifies kernel and IP placement, reducing soft logic needed for connectivity</li> <li>Streamlines programming experience for software and hardware developers</li> </ul>                                                                                             |

## **BENCHMARK**

#### 1.6Tb/s Example: SmartPHY for DCI and Transport Application

Shown below is a comparison of estimated power consumption of an equivalent DCI Bridging design on Versal Premium devices vs. the projected performance of competing programmable devices. Versal architectural features, e.g., high-density, hardened Ethernet interfaces, crypto engines, and best in-class 112G PAM4 SerDes technology, drive a 2.2X better performance-per-watt against the equivalent Intel Agilex 10nm FPGA implementation. In addition, the Versal Premium VP1402 can scale to 2.4Tb/s in a single device, achieving even greater performance, area, and power advantages.

Intel Agilex I series device with 200G half-duplex crypto was not available in the tools

Versal Premium features multiple hardened 400G High-Speed Crypto Engines – no programmable logic required

Based on Quartus Power & Thermal Calculator 2021.2 including SmartVID and static power savings, Xilinx XPE 2020.3

For ease of comparison, the example is limited to 1.6Tb/s throughput

## TAKE THE NEXT STEP

- > To learn more about the breakthrough integration of Versal Premium series, watch the video

- > To try the above benchmark yourself, visit www.xilinx.com/versal-performance-elevated

- > For more information on the Versal Premium series, visit <u>www.xilinx.com/versal-premium</u>

- > To apply to the Versal Premium Evaluation Kit Early Access Program, visit Contact Sales

#### DISCLAIMERS

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### COPYRIGHT NOTICE

© 2023 Advanced Micro Devices, Inc. All rights reserved. Xilinx, the Xilinx logo, AMD, the AMD Arrow logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCIe, and PCI Express are trademarks of PCI-SIG and used under license. PID# 231846771-I

## AMD, READY TO CONNECT? VISIT xilinx.com/versal-premium