# **ALVEO™ U25N SmartNIC**

ネットワークおよびセキュリティの高速化を可能にする 2x25GbE SmartNIC ターンキーソリューション

# 概要

Alveo U25N は、最新データセンターの構築を進めるクラウドおよびエンタープライズアーキテクト向けの包括的な SmartNIC プラットフォームで、単一プラットフォームにネットワークとセキュリティアクセラレーション機能を統合したソリューションを提供します。

U25N SmartNIC プラットフォームには、実証済みの XtremeScale<sup>™</sup> X2 イーサネット コントローラー、ザイリンクス UltraScale+<sup>™</sup> FPGA、マルチコア Arm プロセッサという 3 つのテクノロジが融合されており、FPGA と Arm プロセッサは画期的なシステム オン チップ (SoC) に統合されています。

FPGA は不要なデータ移動を排除して最大限の効率化を図りながらハードウェアでの高速化とオフロードを実現します。Arm コアは、例外トラフィック処理や FPGA 関連の管理および統計処理に対応します。X2 イーサネット コントローラー チップは、フィールド実証済みのソフトウェアドライバーを介して、2 ポートの 25 ギガビット イーサネットを処理するためのプラットフォームを提供します。

# 機能と利点

パ**ワフルな SmartNIC** - U25N は、超高スループット、小パケット性能、低レイテンシを実現できます。ホスト インターフェイスは、標準 NIC ドライバーをサポートに加えて、Onload® カーネル バイパスをサポートし、TCP およびパケットベースの両方の API を提供して、ネットワーク アプリケーションの高速化を可能にします。U25N は耐タンパー性を備え、ステートレス ファイアウォールで実行されるセキュアなフロー監視機能もサポートしています。

プログラム可能なプラットフォーム - U25N SmartNIC には、すべてのネットワーク フローを処理するプログラム可能な FPGA が搭載されています。各フローを個別にホストに配信したり、BITW (Bump In The Wire) 方式のネットワーク アクセラレーション機能を使用して、ハードウェアにストリーミングすることが可能です。また、独自のワークロードを高速化することも可能です。

**クラウド向けのハードウェア アクセラレーション** - クラウド サービス プロバイダーは、SmartNIC ファブリックを運用することで、CPU コアおよびネットワーク リンクに比例して 増大する仮想スイッチやサービスのマイクロセグメンテーションに対応できます。U25N は、パッケージ化されたアプリケーションを含む、業界初の統合 SmartNIC ファブリック向けのプラットフォームです。

# ザイリンクスの優位性

- > Bump-In-The-Wire (BITW) モデルによる、ネット ワークおよびセキュリティ機能のオフロードとアク セラレーション

- > Open vSwitch (OvS)、IPsec、ファイアウォール、 QoS を含む、ターンキーの先進ネットワーク アクセ ラレーション

- アプリケーションのカスタマイズとプログラマビリ ティを活かした、カスタムワークロードの柔軟な 追加

- > 実績ある XtremeScale™ イーサネット コントローラーと同等のベースライン NIC 機能

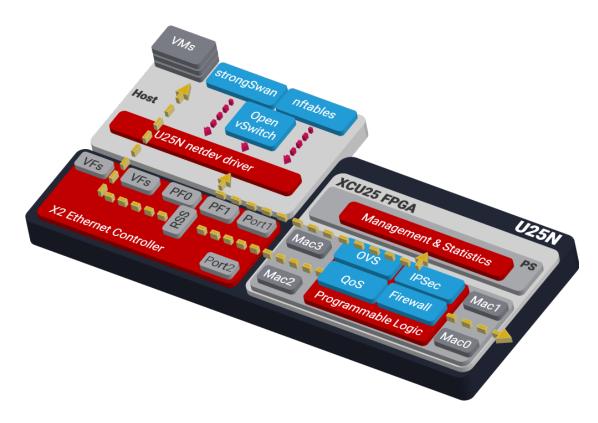

U25N のアーキテクチャ ブロック図

# U25N のプラットフォーム アーキテクチャ

U25N は、X2 イーサネット コントローラー、PS ブロックの Arm コア、FPGA プログラマブル ロジック (PL) という 3 つのコンピューテーショナル コンポーネントで構成されます。

U25N SmartNIC のデータ プレーン処理タスクは、大半が X2 または FPGA 内で処理されます。どちらのブロックも、25 Gbps/ポートのワイヤ レートでトラフィックを処理するように設計されています。X2 は、標準ネットワーク タスクを処理するほかに、SR-IOV (Single Root I/O Virtualization) 要求を処理して、物理機能 (PF) と仮想機能 (VF) をセットアップします。

FPGA には、いくつかのデータ プレーン パイプライン ステージがあります。これらのパイプライン ステージには、マッチ アクション エンジン (MAE) が含まれており、VXLAN や L2GRE のようなネットワーク仮想化タスクを実行します。

Internet Protocol Security (IPsec) ブロックは、strongSwan アプリケーションを利用してルールを設定することで、プロトコル処理の IPsecレイヤーをオフロードします。また、FPGA 内でステートレス ファイアウォールを実行し、ホストの nftables エントリから渡されたルールをサポートします。さらに、階層型トークン バケット (HTB) の実装によりサービス品質(QoS)をサポートし、エグレストラフィックシェーピングと優先制御を確実に実行します。

U25N の Arm コアは、主に、FPGA プログラマブル ロジックのホスト CPU からコントロール プレーン管理トラフィックを受け取る管理エージェントとして使用されます。Arm コアで実行されるエージェント アプリケーションが、これらプログラム ロジック ブロックの実行中に、MAE、IPsec、ファイアウォールで使用されるテーブルを更新します。また、U25N SmartNIC プラットフォーム内の全般的な処理を向上するために使用される各種の統計を収集します。

# 機能

### ネットワーク アクセラレーション

- > DPDK ポール モード ドライバー パケット (クラウド、テレコム)

- > Onload® TCP (クラウド、テレコム、エンタープライズ)

- > Onload®/TCPDirect TCP/UDP (フィンテック)

### ステートレス オフロード

- > TCP/UDP チェックサム オフロード (CSO)、TCP セグメンテーション オフロード (TSO)、Giant Send オフロード (GSO)

- > ラージ センド オフロード (LSO)、ラージ レシーブ オフロード (LRO)、 レシーブ サイド スケーリング (RSS)

- > 受信セグメント統合 (RSC)

# ハードウェアベースのパケット処理

- > オープン仮想スイッチ (OVS) データ プレーン オフロード

- > コネクショントラッキング (ステートフル ファイアウォール)

- 確実なエグレストラフィックシェーピングと優先制御を可能にする サービス品質(OoS)

#### セキュリティ

- > ハードウェアでの IPsec 暗号化 /復号化

- ・AES-GCM 256 ビットキー

- > strongSwan プラグインによる IPsec オフロード サポート

- > nftables によるハードウェア アクセラレーション フィルタリング

- 耐タンパー性を備えた X2 ファームウェア 秘密キーを使用したデジタル 署名および保護

### 管理性能とリモート ブート

> UFFI

#### 管理とユーティリティ

- > Ethtool のサポート

- > ブートマネージャー

#### アダプター ハードウェア

- > ホストへの PCIe Gen 3 x8 インターフェイス (Gen 3 x16 PCIe コネクタ)

- > 2x10/25G SFP28 DA 銅線または光トランシーバー

- > XtremeScale™ X2 イーサネット コントローラー

- > Zynq® UltraScale+™ XCU25N FPGA

- > 1x 2GB x 40 DDR4-2666 (Arm コア使用)

- > 1x 4GB x 72 DDR4-2666 (FPGA 使用)

#### 次のステップ

#### トラフィック エンジニアリング

- > XtremePacket™ エンジン (解析、フィルタリング、フロー ステアリング)

- > TCP/UDP/IP、MAC、VLAN、RSS フィルタリング、アクセラレーション 受信フロー ステアリング (ARFS)、送信パケット ステアリング

#### 仮想化

- > Linux マルチキュー

- > SR-IOV: 2 つの物理機能 (PF)、240 の仮想機能 (VF)

- > VXLAN、L2GRE トンネリング オフロード、カスタム オーバーレイに適 応可能

### イーサネット規格

- > IEEE802.3-2018 イーサネット ベース規格

- > IEEE 802.3by イーサネット コンソーシアム 25 ギガビット イーサネット

- > IEEE 802.3ad、802.1AX リンク アグリゲーション

- > IEEE 802.1Q、802.1P VLAN タグおよび優先順位

- > ジャンボ フレーム サポート (9000 バイト)

#### OS サポート

> Ubuntu、Red Hat RHEL、Linux バリアント

#### 寸法

- > 長さ: 6.60 インチ (167.65mm)

- > 幅: 2.54 インチ (64.4mm)

#### ハードウェア認証

- > FCC、UL、CE

- > RoHS EU 指令 2011/65/EU に準拠

#### 環境要件

#### 温度:

> 動作時: 0°C~55°C (32°F~131°F)

> 保管時: -40°C ~ 65°C (-40°F ~ 149°F)

### 湿度:

> 動作時: 10% ~ 80%

> 保管時:5%~90%

#### 製品注文情報

> A-U25N-P06G-PQ-G

注記:

使用できる機能は、ソフトウェア リリースによって異なります。詳細は、リリース ノートをご確認いただくか、 <u>ザイリンクス サポート</u>にお問い合わせください。

本社

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 USA 電話: 408-559-7778 www.xilinx.com ヨーロッパ

Bianconi Avenue Citywest Business Campus Saggart, County Dublin Ireland 電話:+353-1-464-0311 www.xilinx.com 日本

ザイリンクス株式会社 141-0032 東京都品川区大崎 1-2-2 アートヴィレッジ大崎 セントラルタワー 4 階 電話: +81-3-6744-7777 iapan.xilinx.com アジア太平洋

Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 電話:+65-6407-3000 www.xilinx.com インド

Xilinx India Technology Services Pvt. Ltd. Block A, B, C, 8th & 13th floors, Meenakshi Tech Park, Survey No. 39 Gachibowli(V), Seri Lingampally (M), Hyderabad -500 084 電話: +91-40-6721-4747 www.xilinx.com

© Copyright 2022 Advanced Micro Devices, Inc. All rights reserved. Xilinx. Xilinx のロゴ、AMD. Arrow のロゴ、Alveo、Arix、Kintex、Kria、Spartan、Versal、Vitis、Virtex、Vivado、Zynq、およびこの文書に含まれるその他の 指定されたプランドは、Advanced Micro Devices, Inc. の商標です。この文書に記載されているその他の製品名は識別自向にのみ使用されており、各社の登録商標です。AMBA、AMBA Designer、Arm、Arm1176JZ-S、CoreSight、Cortex、 PrimeCell はも日まよびその他各国の Arm 社の登録商標です。PCIe、および PCI Express は PCI-SIG の商標であり、ライセンスに基づいて使用されています。