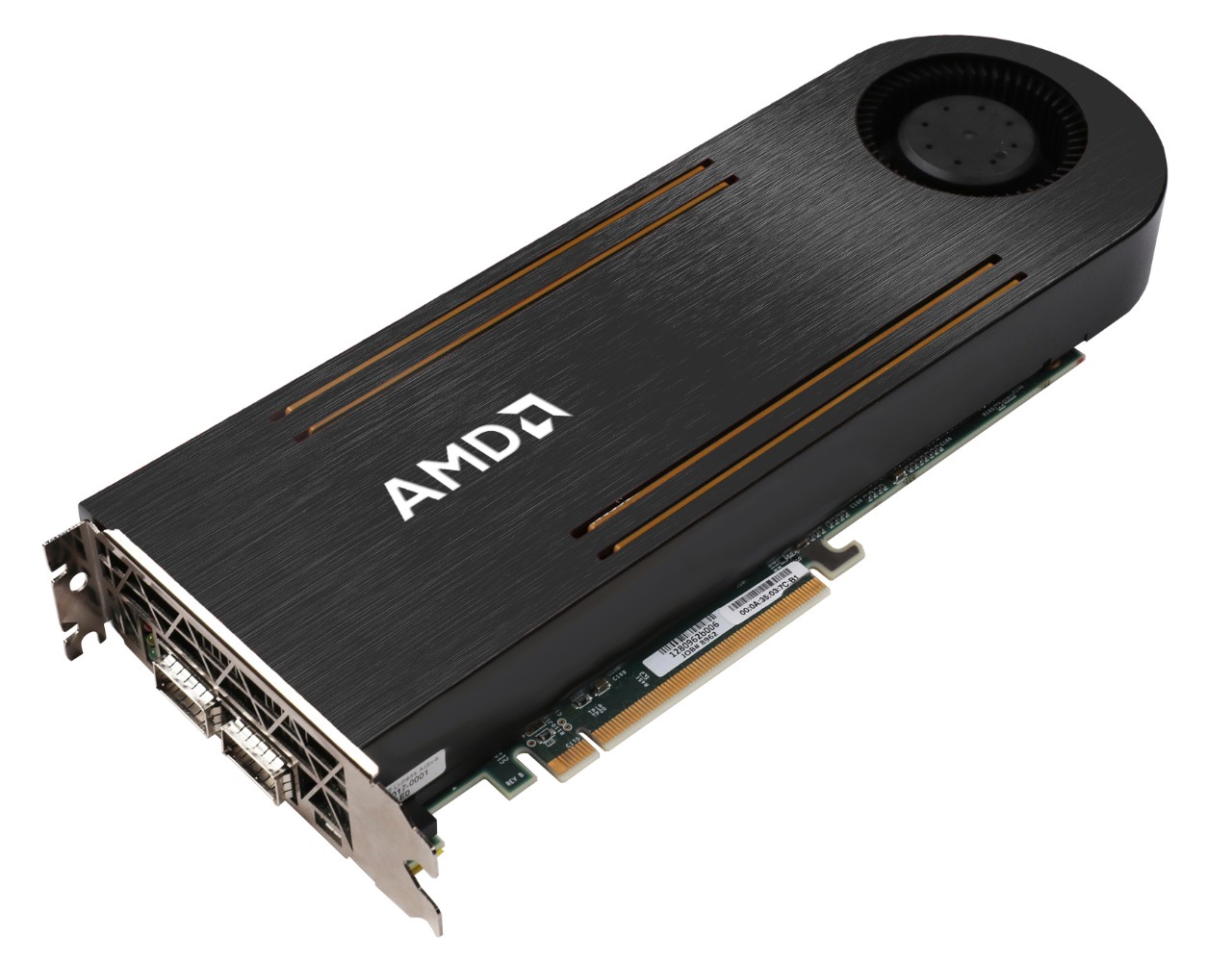

AMD Virtex UltraScale+ FPGA VCU1525 アクセラレーション開発キット

Virtex UltraScale+ FPGA アクセラレーション開発キットは、ハイパースケール アプリケーションの開発を始めるにあたって最適な環境を提供します。

概要

重要なお知らせ:

この開発キットは、 製造中止製品の通知 XCN18025 により、製造中止となっています。この製品を対象としたソリューションが更新される予定はありません。今後、AMD のサポートは制限されます。

製品説明

Virtex™ UltraScale+™ FPGA の高度な機能を活用するデータセンター アプリケーション開発者に理想的なキットです。この PCIe® 開発ボードは、AMD の SDAccel™ 開発環境で OpenCL™、C、C++、および RTL を使用した簡単なアプリケーション プログラミングをサポートするためのフレームワーク、ライブラリ、ドライバー、開発ツールと共に、クラウドおよびオンプレミスで利用できます。

主な機能と利点

- 演算負荷の高いアプリケーションに特化した再プログラム可能なハードウェア、特にライブ ビデオのトランスコーディング、データ解析、ゲノミクス、機械学習などの急成長市場をターゲットとする

- フルレングス、フルハイト フォーム ファクターのデュアル スロット PCIe に準拠

- 最大 225W 対応のボードを使用して、サーバー CPU の 10 ~ 100 倍の性能アクセラレーションを実現

- カスタム ボードをサポートする SDAccel プラットフォーム リファレンス デザイン

- OpenCL、C、C++、および RTL に対応する SDAccel™ 開発環境でサポート

- VU9P Virtex UltraScale+ FPGA

- 21 TOP (8 ビット整数精度)

- 346Mb オンチップ メモリ

- 64GB オンボード DDR4 DIMM メモリ

AMD デバイス

XCVU9P-L2FSGD2104E FPGA の特長

| システム ロジック セル (K) | 2,586 |

|---|---|

| DSP スライス | 6,840 |

| メモリ (Mb) | 345.9 |

| GTY 32.75Gb/s トランシーバー | 76 |

| I/O | 676 |

製品情報

ボードの機能

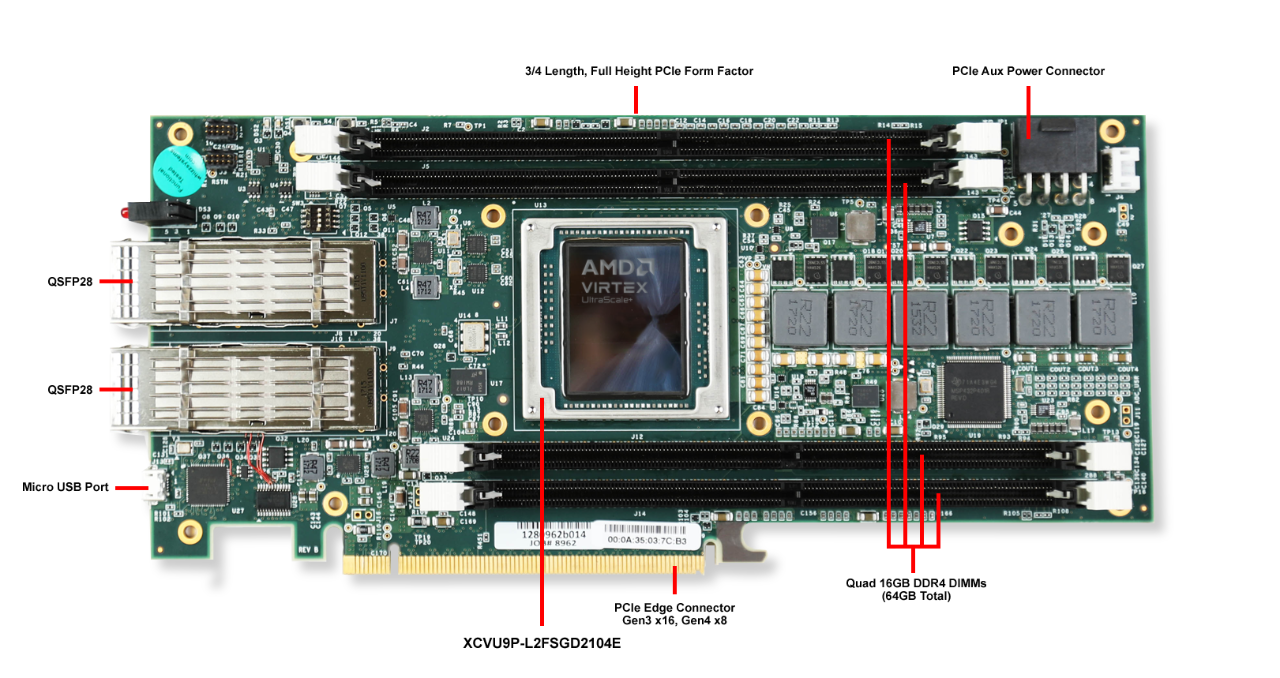

VCU1525 ボードの特長

メモリ

- 4 ~ 16GB DDR4 DIMM

消費電力と熱

- アクティブ冷却

- 225W の最大ダイナミック パワー ソーシング

- PCIe エッジ コネクタから最大 75W

- PCIe 補助電源コネクタからさらに最大 150W

コンフィギュレーション

- Micro USB ポートを使用して JTAG 経由での FPGA コンフィギュレーション

- QSPI コンフィギュレーション フラッシュ メモリ

通信およびネットワーク

- 2 つの QSFP28 100G インターフェイス

- PCIe Gen3 x 16 または Gen4 x8 (エッジ コネクタを使用)

AMD デバイス

XCVU9P-L2FSGD2104E FPGA の特長

| システム ロジック セル (K) | 2,586 |

|---|---|

| DSP スライス | 6,840 |

| メモリ (Mb) | 345.9 |

| GTY 32.75Gb/s トランシーバー | 76 |

| I/O | 676 |

内容

VCU1525 ボード (XCVU9P-L2FSGD2104E)

Vivado™ Design Suite: Design Edition バウチャー コード

ノードはロックされ、ターゲット デバイスは XCVU9P FPGA にロック (1 年間のアップデート付き)

USB Micro ケーブル

リソース

デザイン ツール

| ツール名 | 詳細 | ライセンス タイプ |

|---|---|---|

| Vivado Design Suite Design Edition | AMD Vivado™ Design Suite は、FPGA および SoC を設計することを目的として開発された IP とシステムを中心とする新しいデザイン環境です。 | ノードはロックされ、ターゲット デバイスは XCVU9P FPGA にロック (1 年間のアップデート付き)。 DFX (Dynamic Function eXchange) をサポート |

| SDAccel 開発環境 | SDAccel は、PCIe® ベースのザイリンクス FPGA アクセラレータ カードをターゲットとする OpenCL アプリケーション向けの開発環境です。この環境では、RTL デザインの知識がなくても、システム プロセッサと FPGA ロジックを同時にプログラムできます。 | ノードはロックされ、ターゲット デバイスは XCVU9P FPGA にロック (1 年間のアップデート付き)。 |

| Dynamic Function eXchange | Dynamic Function eXchange は、パーシャル ビット ファイルをダウンロードしてロジック ブロックを動的に修正する機能で、そのほかロジックは中断せずにそのまま保持できます。AMD のパーシャル リコンフィギュレーション技術では、アクセラレータ ボードの機能をオンザフライで変更できるため、リローディング時にすべての PCIe リンクを再設定および再確立する必要がありません。 | ノードはロックされ、ターゲット デバイスは XCVU9P FPGA にロック (1 年間のアップデート付き)。 |

IP

| ツール名 | 詳細 | ライセンス タイプ |

|---|---|---|

| DDR4 SDRAM Controller | DDR4 SDRAM コントローラーは、 Vivado IP カタログでは、無償 IP コアです。 | 無償 IP |

| DMA for PCI Express (PCIe) Subsystem | AMD LogiCORE™ の QDMA for PCI Express (PCIe) は、PCI Express 3.x 統合ブロックで使用するための高性能で設定可能な Scatter Gather DMA を実装します。この IP は、オプションで AXI4-MM または AXI4-Stream ユーザー インターフェイスを提供します。 | 無償 IP |

| AMD SmartConnect テクノロジ | AMD の SmartConnect テクノロジは、高集積で数百万個のシステム ロジック セルを含むデザインにおけるシステム レベルのインターコネクト ボトルネックを解消するため、UltraScale+™ デバイス ポートフォリオにかつてないレベルの性能向上をもたらします。 | 無償 IP |

| カスタム ボード サポート用の SDAccel プラットフォーム リファレンス デザイン | SDAccel のプロジェクトは、ターゲット プラットフォーム用にコンパイルされます。SDAccel プラットフォーム リファレンス デザインは、ボードおよびハードウェア/ソフトウェアの基礎構造コンポーネントで構成されており、HW/SW コンポーネントでは、OpenCL アプリケーションのカーネルが実行されます。 このリファレンス デザインは、プラットフォーム開発者が独自のカスタム PCIe ボードに SDAccel サポートを追加するためのスターティング ポイントとして使用することを目的としています。 | 無償 IP |

VCU1525 アクセラレータ カードをセットアップ

2018.3

ザイリンクス ランタイムおよび運用シェルをダウンロードし、

1.

ザイリンクス ランタイムをダウンロード

ザイリンクス ランタイム (XRT) は、ホストとカード間の下位通信レイヤー (API とドライバー) です。

重要: XRT をインストールする前に次のコマンドを入力してください。

RedHat:

$ sudo yum-config-manager --enable rhel-7-server-optional-rpms

$ sudo yum install -y https://dl.fedoraproject.org/pub/epel/epel-release-latest-7.noarch.rpm

CentOS:

$ sudo yum install epel-release

2.

運用シェルをダウンロード

運用シェルは、物理的に実装された通信レイヤーであり、カードへの書き込みを実行します。

注記:

VCU1525 では、アプリケーション開発にこのシェルを使用します。このカード自体は開発専用であり、エンド システムの一部としての量産運用には認定されていません。

VCU1525 アクセアレーションを利用するアプリケーションを開発

開発者の方は、これらの追加ファイルをダウンロードし、入門ガイドに従ってインストールしてください。

3.

開発シェルをダウンロード

独自のアプリケーションを構築する場合は、開発用シェル インターフェイスが必要です。

4.

SDAccel デザイン環境のダウンロード

AMD SDAccel IDE は、高速化されたアプリケーション開発用のフレームワークを提供します。